インテルのみ表示可能 — GUID: hco1416492114993

Ixiasoft

1. リリース情報

2. 外部メモリー・インターフェイス・ インテル® Stratix® 10 FPGA IPの概要

3. インテル® Stratix® 10 EMIF IPの製品アーキテクチャー

4. インテル® Stratix® 10 EMIF IPにおけるエンドユーザーの信号

5. インテル® Stratix® 10 EMIF – メモリーIPのシミュレーション

6. DDR3における インテル® Stratix® 10 EMIF IP

7. DDR4における インテル® Stratix® 10 EMIF IP

8. QDR II/II+/II+ Xtremeにおける インテル® Stratix® 10 EMIF IP

9. QDR-IVにおける インテル® Stratix® 10 EMIF IP

10. RLDRAM 3における インテル® Stratix® 10 EMIF IP

11. インテル® Stratix® 10 EMIF IPにおけるタイミング・クロージャー

12. コントローラー性能の最適化

13. インテル® Stratix® 10 EMIF IPのデバッグ

14. 外部メモリー・インターフェイス・ インテル® Stratix® 10 FPGA IPユーザーガイドのアーカイブ

15. 外部メモリー・インターフェイス・ インテル® Stratix® 10 FPGA IPユーザーガイドの改訂履歴

3.1. インテル® Stratix® 10 EMIFのアーキテクチャー: 概要

3.2. インテル® Stratix® 10 EMIFシーケンサー

3.3. インテル® Stratix® 10 EMIFのキャリブレーション

3.4. インテルStratix 10 EMIF IPコントローラー

3.5. 複数の インテル® Stratix® 10 EMIFでのハードウェア・リソースの共有

3.6. インテル® Stratix® 10 EMIF IPでのユーザーによって要求されるリセット

3.7. ハード・プロセッサー・サブシステムに向けての インテル® Stratix® 10 EMIF

3.8. インテル® Stratix® 10 EMIFピンポンPHY

3.1.1. インテル® Stratix® 10 EMIFのアーキテクチャー: I/Oサブシステム

3.1.2. インテル® Stratix® 10 EMIFのアーキテクチャー: I/O列

3.1.3. インテル® Stratix® 10 EMIFのアーキテクチャー: I/O SSM

3.1.4. インテル® Stratix® 10 EMIFのアーキテクチャー: I/Oバンク

3.1.5. インテル® Stratix® 10 EMIFのアーキテクチャー: I/Oレーン

3.1.6. インテル® Stratix® 10 EMIFのアーキテクチャー: 入力DQSクロックツリー

3.1.7. インテル® Stratix® 10 EMIFのアーキテクチャー: PHYクロックツリー

3.1.8. インテル® Stratix® 10 EMIFのアーキテクチャー: PLLリファレンス・クロック・ネットワーク

3.1.9. インテル® Stratix® 10 EMIFのアーキテクチャー: クロックの位相アライメント

4.1.1.1. DDR3のlocal_reset_req

4.1.1.2. DDR3のlocal_reset_status

4.1.1.3. DDR3のpll_ref_clk

4.1.1.4. DDR3のpll_locked

4.1.1.5. DDR3のpll_extra_clk_0

4.1.1.6. DDR3のpll_extra_clk_1

4.1.1.7. DDR3のpll_extra_clk_2

4.1.1.8. DDR3のpll_extra_clk_3

4.1.1.9. DDR3のoct

4.1.1.10. DDR3のmem

4.1.1.11. DDR3のstatus

4.1.1.12. DDR3のafi_reset_n

4.1.1.13. DDR3のafi_clk

4.1.1.14. DDR3のafi_half_clk

4.1.1.15. DDR3のafi

4.1.1.16. DDR3のemif_usr_reset_n

4.1.1.17. DDR3のemif_usr_clk

4.1.1.18. DDR3のemif_usr_reset_n_sec

4.1.1.19. DDR3のemif_usr_clk_sec

4.1.1.20. DDR3のcal_debug_reset_n

4.1.1.21. DDR3のcal_debug_clk

4.1.1.22. DDR3のcal_debug_out_reset_n

4.1.1.23. DDR3のcal_debug_out_clk

4.1.1.24. DDR3のclks_sharing_master_out

4.1.1.25. DDR3のclks_sharing_slave_in

4.1.1.26. DDR3のclks_sharing_slave_out

4.1.1.27. DDR3のctrl_amm

4.1.1.28. DDR3のctrl_auto_precharge

4.1.1.29. DDR3のctrl_user_priority

4.1.1.30. DDR3のctrl_ecc_user_interrupt

4.1.1.31. DDR3のctrl_ecc_readdataerror

4.1.1.32. DDR3のctrl_mmr_slave

4.1.1.33. DDR3のhps_emif

4.1.1.34. DDR3のcal_debug

4.1.1.35. DDR3のcal_debug_out

4.1.2.1. DDR4のlocal_reset_req

4.1.2.2. DDR4のlocal_reset_status

4.1.2.3. DDR4のpll_ref_clk

4.1.2.4. DDR4のpll_locked

4.1.2.5. DDR4のpll_extra_clk_0

4.1.2.6. DDR4のpll_extra_clk_1

4.1.2.7. DDR4のpll_extra_clk_2

4.1.2.8. DDR4のpll_extra_clk_3

4.1.2.9. DDR4のoct

4.1.2.10. DDR4のmem

4.1.2.11. DDR4のstatus

4.1.2.12. DDR4のafi_reset_n

4.1.2.13. DDR4のafi_clk

4.1.2.14. DDR4のafi_half_clk

4.1.2.15. DDR4のafi

4.1.2.16. DDR4のemif_usr_reset_n

4.1.2.17. DDR4のemif_usr_clk

4.1.2.18. DDR4のemif_usr_reset_n_sec

4.1.2.19. DDR4のemif_usr_clk_sec

4.1.2.20. DDR4のcal_debug_reset_n

4.1.2.21. DDR4のcal_debug_clk

4.1.2.22. DDR4のcal_debug_out_reset_n

4.1.2.23. DDR4のcal_debug_out_clk

4.1.2.24. DDR4のclks_sharing_master_out

4.1.2.25. DDR4のclks_sharing_slave_in

4.1.2.26. DDR4のclks_sharing_slave_out

4.1.2.27. DDR4のctrl_amm

4.1.2.28. DDR4のctrl_auto_precharge

4.1.2.29. DDR4のctrl_user_priority

4.1.2.30. DDR4のctrl_ecc_user_interrupt

4.1.2.31. DDR4のctrl_ecc_readdataerror

4.1.2.32. DDR4のctrl_mmr_slave

4.1.2.33. DDR4のhps_emif

4.1.2.34. DDR4のcal_debug

4.1.2.35. DDR4のcal_debug_out

4.1.3.1. QDR II/II+/II+ Xtremeのlocal_reset_req

4.1.3.2. QDR II/II+/II+ Xtremeのlocal_reset_status

4.1.3.3. QDR II/II+/II+ Xtremeのpll_ref_clk

4.1.3.4. QDR II/II+/II+ Xtremeのpll_locked

4.1.3.5. QDR II/II+/II+ Xtremeのpll_extra_clk_0

4.1.3.6. QDR II/II+/II+ Xtremeのpll_extra_clk_1

4.1.3.7. QDR II/II+/II+ Xtremeのpll_extra_clk_2

4.1.3.8. QDR II/II+/II+ Xtremeのpll_extra_clk_3

4.1.3.9. QDR II/II+/II+ Xtremeのoct

4.1.3.10. QDR II/II+/II+ Xtremeのmem

4.1.3.11. QDR II/II+/II+ Xtremeのstatus

4.1.3.12. QDR II/II+/II+ Xtremeのemif_usr_reset_n

4.1.3.13. QDR II/II+/II+ Xtremeのemif_usr_clk

4.1.3.14. QDR II/II+/II+ Xtremeのcal_debug_reset_n

4.1.3.15. QDR II/II+/II+ Xtremeのcal_debug_clk

4.1.3.16. QDR II/II+/II+ Xtremeのcal_debug_out_reset_n

4.1.3.17. QDR II/II+/II+ Xtremeのcal_debug_out_clk

4.1.3.18. QDR II/II+/II+ Xtremeのclks_sharing_master_out

4.1.3.19. QDR II/II+/II+ Xtremeのclks_sharing_slave_in

4.1.3.20. QDR II/II+/II+ Xtremeのclks_sharing_slave_out

4.1.3.21. QDR II/II+/II+ Xtremeのctrl_amm

4.1.3.22. QDR II/II+/II+ Xtremeのcal_debug

4.1.3.23. QDR II/II+/II+ Xtremeのcal_debug_out

4.1.4.1. QDR-IVのlocal_reset_req

4.1.4.2. QDR-IVのlocal_reset_status

4.1.4.3. QDR-IVのpll_ref_clk

4.1.4.4. QDR-IVのpll_locked

4.1.4.5. QDR-IVのpll_extra_clk_0

4.1.4.6. QDR-IVのpll_extra_clk_1

4.1.4.7. QDR-IVのpll_extra_clk_2

4.1.4.8. QDR-IVのpll_extra_clk_3

4.1.4.9. QDR-IVのoct

4.1.4.10. QDR-IVのmem

4.1.4.11. QDR-IVのstatus

4.1.4.12. QDR-IVのafi_reset_n

4.1.4.13. QDR-IVのafi_clk

4.1.4.14. QDR-IVのafi_half_clk

4.1.4.15. QDR-IVのafi

4.1.4.16. QDR-IVのemif_usr_reset_n

4.1.4.17. QDR-IVのemif_usr_clk

4.1.4.18. QDR-IVのcal_debug_reset_n

4.1.4.19. QDR-IVのcal_debug_clk

4.1.4.20. QDR-IVのcal_debug_out_reset_n

4.1.4.21. QDR-IVのcal_debug_out_clk

4.1.4.22. QDR-IVのclks_sharing_master_out

4.1.4.23. QDR-IVのclks_sharing_slave_in

4.1.4.24. QDR-IVのclks_sharing_slave_out

4.1.4.25. QDR-IVのctrl_amm

4.1.4.26. QDR-IVのcal_debug

4.1.4.27. QDR-IVのcal_debug_out

4.1.5.1. RLDRAM 3のlocal_reset_req

4.1.5.2. RLDRAM 3のlocal_reset_status

4.1.5.3. RLDRAM 3のpll_ref_clk

4.1.5.4. RLDRAM 3のpll_locked

4.1.5.5. RLDRAM 3のpll_extra_clk_0

4.1.5.6. RLDRAM 3のpll_extra_clk_1

4.1.5.7. RLDRAM 3のpll_extra_clk_2

4.1.5.8. RLDRAM 3のpll_extra_clk_3

4.1.5.9. RLDRAM 3のoct

4.1.5.10. RLDRAM 3のmem

4.1.5.11. RLDRAM 3のstatus

4.1.5.12. RLDRAM 3のafi_reset_n

4.1.5.13. RLDRAM 3のafi_clk

4.1.5.14. RLDRAM 3のafi_half_clk

4.1.5.15. RLDRAM 3のafi

4.1.5.16. RLDRAM 3のcal_debug_reset_n

4.1.5.17. RLDRAM 3のcal_debug_clk

4.1.5.18. RLDRAM 3のcal_debug_out_reset_n

4.1.5.19. RLDRAM 3のcal_debug_out_clk

4.1.5.20. RLDRAM 3のclks_sharing_master_out

4.1.5.21. RLDRAM 3のclks_sharing_slave_in

4.1.5.22. RLDRAM 3のclks_sharing_slave_out

4.1.5.23. RLDRAM 3のcal_debug

4.1.5.24. RLDRAM 3のcal_debug_out

4.4.1. ctrlcfg0

4.4.2. ctrlcfg1

4.4.3. dramtiming0

4.4.4. caltiming0

4.4.5. caltiming1

4.4.6. caltiming2

4.4.7. caltiming3

4.4.8. caltiming4

4.4.9. caltiming9

4.4.10. dramaddrw

4.4.11. sideband0

4.4.12. sideband1

4.4.13. sideband4

4.4.14. sideband6

4.4.15. sideband7

4.4.16. sideband9

4.4.17. sideband11

4.4.18. sideband12

4.4.19. sideband13

4.4.20. sideband14

4.4.21. dramsts

4.4.22. niosreserve0

4.4.23. niosreserve1

4.4.24. sideband16

4.4.25. ecc3: ECCエラーおよび割り込みコンフィグレーション

4.4.26. ecc4: ステータスとエラー情報

4.4.27. ecc5: 最新のSBEまたはDBEのアドレス

4.4.28. ecc6: 最新の見送られた訂正コマンドのアドレス

4.4.29. ecc7: 最新のSBEまたはDBEのアドレスの拡張

4.4.30. sc8: 最新の見送られた訂正コマンドのアドレスの拡張

6.1.1. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: General

6.1.2. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: FPGA I/O

6.1.3. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Memory

6.1.4. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Mem I/O

6.1.5. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Mem Timing

6.1.6. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Board

6.1.7. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Controller

6.1.8. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Diagnostics

6.1.9. インテルStratix 10 EMIF IPにおけるDDR3のパラメーター: Example Designs

7.1.1. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: General

7.1.2. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: FPGA I/O

7.1.3. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Memory

7.1.4. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Mem I/O

7.1.5. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Mem Timing

7.1.6. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Board

7.1.7. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Controller

7.1.8. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Diagnostics

7.1.9. インテルStratix 10 EMIF IPにおけるDDR4のパラメーター: Example Designs

8.1.1. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: General

8.1.2. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: FPGA I/O

8.1.3. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Memory

8.1.4. インテル Stratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Mem Timing

8.1.5. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Board

8.1.6. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Controller

8.1.7. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Diagnostics

8.1.8. インテルStratix 10 EMIF IPにおけるQDR II/II+/II+ Xtremeのパラメーター: Example Designs

9.1.1. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: General

9.1.2. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: FPGA I/O

9.1.3. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Memory

9.1.4. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Mem Timing

9.1.5. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Board

9.1.6. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Controller

9.1.7. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Diagnostics

9.1.8. インテルStratix 10 EMIF IPにおけるQDR-IVのパラメーター: Example Designs

10.1.1. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: General

10.1.2. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: FPGA I/O

10.1.3. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Memory

10.1.4. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Mem Timing

10.1.5. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Board

10.1.6. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Controller

10.1.7. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Diagnostics

10.1.8. インテルStratix 10 EMIF IPにおけるRLDRAM 3のパラメーター: Example Designs

13.7.1.1. ユーザー・インターフェイス

13.7.1.2. 通信

13.7.1.3. セットアップと使用

13.7.1.4. EMIF IPをデバッグ・ツールキットで使用するためのコンフィグレーション

13.7.1.5. レポート

13.7.1.6. オンダイ終端のキャリブレーション

13.7.1.7. アイ・ダイアグラム

13.7.1.8. インテル® Stratix® 10 EMIF IPに向けたドライバーを使用するマージン調整

13.7.1.9. EMIFデバッグ・ツールキットを実行するためのTclスクリプト例

13.7.1.10. インテル® Stratix® 10 HPSインターフェイスでのEMIFデバッグ・ツールキットの使用

インテルのみ表示可能 — GUID: hco1416492114993

Ixiasoft

12.4.5. アディティブ・レイテンシーとバンク・インターリーブ

アディティブ・レイテンシーをバンク・インターリーブとともに使用することで、コントローラーの帯域幅が拡大します。

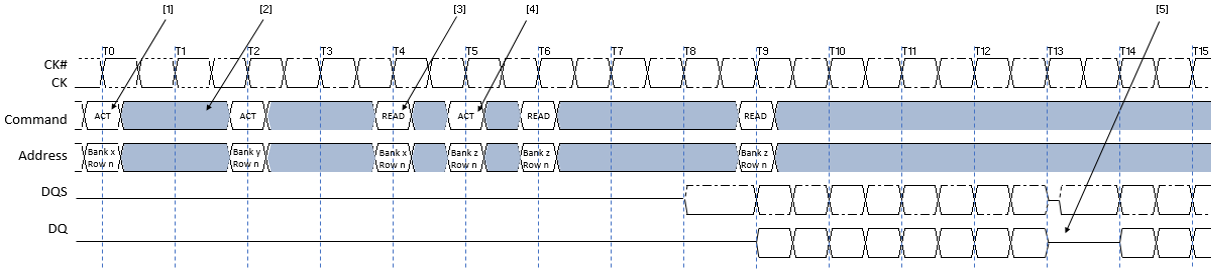

次の図は、読み出し動作でのアディティブ・レイテンシーなしのバンク・インターリーブの例を示しています。この例では、CASレイテンシーが5、バースト長が8のバンク・インターリーブの読み出しを使用しています。

図 101. バンク・インターリーブ (アディティブ・レイテンシーなし)

次の一連のイベントは、上の図を説明しています。

- コントローラーはアクティブ化コマンドを発行してバンクを開きます。ここではバンクxとそのバンクの行をアクティブ化します。

- tRCD時間の後、コントローラーはオートプリチャージの読み出しコマンドを指定されたバンクに発行します。

- バンクyは、tRRD時間の後にアクティブ化コマンドを受信します。

- コントローラーはバンクxがオートプリチャージの読み出しコマンドを受信するまで待機する必要があるため、バンクzに最適な位置でアクティブ化コマンドを発行できません。そのため、アクティブ化コマンドを1クロックサイクル遅らせます。

- アクティブ化コマンドの遅延により、メモリーデバイスからの出力データにギャップが生じます。

注: アディティブ・レイテンシーの1を使用する場合、レイテンシーは読み出しコマンドにのみ影響し、書き込みコマンドのタイミングには影響しません。

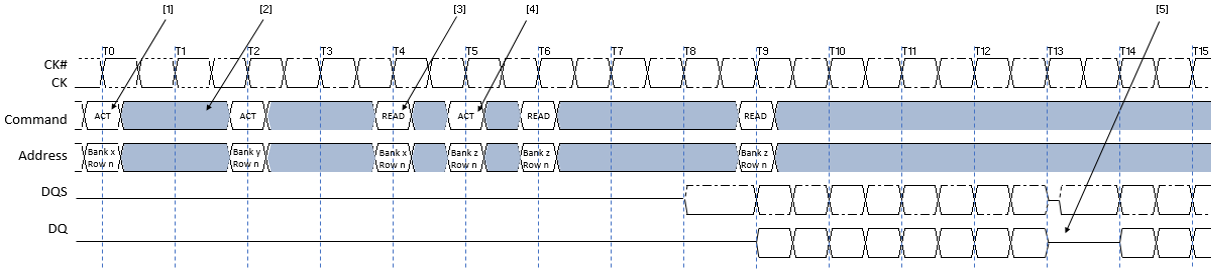

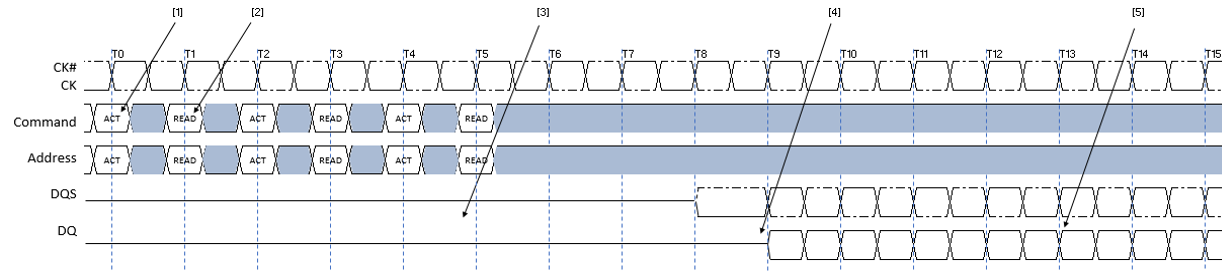

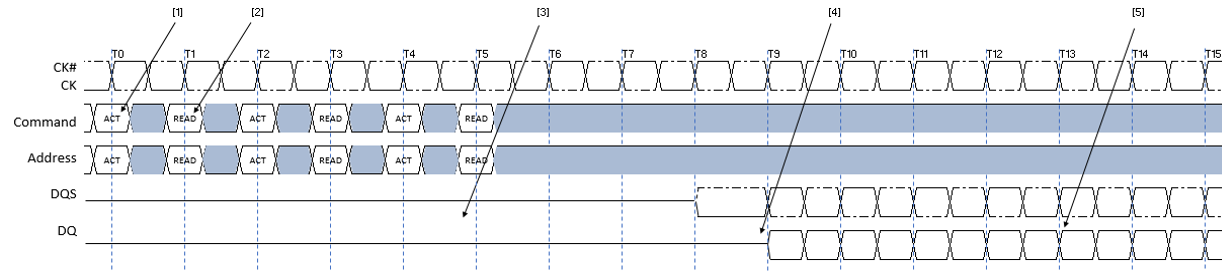

次の図は、読み出し動作におけるアディティブ・レイテンシーをともなうバンク・インターリーブの例を示しています。この例では、アディティブ・レイテンシーが3、CASレイテンシーが5、バースト長が8のバンク・インターリーブ読み出しを使用します。このコンフィグレーションでは、コントローラーはアクティブ化コマンドとオートプリチャージの読み出しコマンドを連続して発行します。

図 102. バンク・インターリーブ (アディティブ・レイテンシーあり)

次の一連のイベントは、上の図を説明しています。

- コントローラーは、バンクxにアクティブ化コマンドを発行します。

- コントローラーは、アクティブ化コマンドの直後にバンクx へのオートプリチャージの読み出しコマンドを発行し、その後、tRCD時間待機します。

- コントローラーは、tRCD後にオートプリチャージの読み出しコマンドを立ち上がりエッジT4で実行します。

- 5サイクルのCASレイテンシーの後、SDRAMデバイスはデータをデータバスに発行します。

- バースト長が8の場合、データ転送には2サイクルが必要です。2クロックでアクティブ化およびオートプリチャージの読み出しコマンドを発行することにより、出力データの連続フローが得られます。

上記の2つの図における効率の結果を比較します。

- アディティブ・レイテンシーなし、CASレイテンシー5、バースト長8のバンク・インターリーブ読み出し (最初の図)

データ転送のアクティブサイクル数= 8

合計サイクル数= 18

効率= 44%

- アディティブ・レイテンシー3、CASレイテンシー4、バースト長4のバンク・インターリーブ読み出し (2番目の図)

データ転送のアクティブサイクル数= 8

合計サイクル数= 17

効率=約47%

アディティブ・レイテンシーをともなうインターリーブ読み出しを使用することで、効率が約3%向上します。

注: アディティブ・レイテンシーにより、連続するインターリーブの読み出しまたは書き込みの効率は向上しますが、ランダムな個々の読み出しまたは書き込みの効率は向上しません。