インテルのみ表示可能 — GUID: xbg1615854170190

Ixiasoft

1. Fタイルの概要

2. Fタイルのアーキテクチャー

3. F-Tile PMA/FEC Direct PHY Intel® FPGA IPの実装

4. F-Tile Reference and System PLL Clocks Intel® FPGA IPの実装

5. FタイルPMA/FEC Direct PHYデザインの実装

6. サポートされるツール

7. Fタイル・トランシーバー・リンクのデバッグ

8. FタイルのアーキテクチャーとPMAおよびFEC Direct PHY IPのユーザーガイド・アーカイブ

9. FタイルのアーキテクチャーとPMAおよびFEC Direct PHY IPのユーザーガイド改訂履歴

A. 付録

2.2.2.1. 400GハードIPとFHTを使用している1つの200GbE-4インターフェイスの実装

2.2.2.2. 400GハードIPとFHTを使用している1つの200GbE-2インターフェイスの実装

2.2.2.3. 400GハードIPとFHTを使用している1つの100GbE-1インターフェイスの実装

2.2.2.4. 400GハードIPとFGTを使用している1つの100GbE-4インターフェイスの実装

2.2.2.5. 200GハードIPとFGTを使用している1つの10GbE-1インターフェイスの実装

2.2.2.6. 400GハードIPとFHTを使用している3つの25GbE-1インターフェイスの実装

2.2.2.7. 400GハードIPとFHTを使用している1つの50GbE-1インターフェイスと2つの25GbE-1インターフェイスの実装

2.2.2.8. 400GハードIPとFHTを使用している1つの100GbE-1インターフェイスと2つの25GbE-1インターフェイスの実装

2.2.2.9. 400GハードIPとFHTを使用している2つの100GbE-1インターフェイスと1つの25GbE-1インターフェイスの実装

2.2.2.10. 400GハードIPとFHTを使用している100GbE-1、100GbE-2、および50GbE-1インターフェイスの実装

3.1. F-Tile PMA/FEC Direct PHY Intel® FPGA IPの概要

3.2. F-Tile PMA/FEC Direct PHY Intel® FPGA IPを使用するデザイン

3.3. IPのコンフィグレーション

3.4. 信号とポートのリファレンス

3.5. PMAおよびFECモードにおけるPHY TXおよびRXデータパスのビットマッピング

3.6. クロック

3.7. カスタム拍生成ポートとロジック

3.8. リセットのアサート

3.9. ボンディングの実装

3.10. 独立したポートのコンフィグレーション

3.11. コンフィグレーション・レジスター

3.12. コンフィグレーション可能な Quartus® Prime開発ソフトウェアの設定

3.13. ハードウェア・テストに向けたF-Tile PMA/FEC Direct PHY Intel® FPGA IPのコンフィグレーション

3.14. Avalon® メモリーマップド・インターフェイスを使用してのハードウェア・コンフィグレーション

3.4.1. TXおよびRXのパラレルおよびシリアル・インターフェイス信号

3.4.2. TXおよびRXのリファレンス・クロックとクロック出力インターフェイス信号

3.4.3. リセット信号

3.4.4. RS-FECの信号

3.4.5. カスタム拍のコントロールおよびステータス信号

3.4.6. TX PMAのコントロール信号

3.4.7. RX PMAのステータス信号

3.4.8. TX/RXのPMAおよびコア・インターフェイスFIFOの信号

3.4.9. PMA Avalon® メモリーマップド・インターフェイスの信号

3.4.10. データパス Avalon® メモリーマップド・インターフェイスの信号

5.1. Fタイル PMA/FEC Direct PHYデザインの実装

5.2. F-Tile PMA/FEC Direct PHY Intel® FPGA IPのインスタンス化

5.3. F-Tile PMA/FEC Direct PHY Intel® FPGA IPでのRS-FEC Directデザインの実装

5.4. F-Tile Reference and System PLL Clocks Intel® FPGA IPのインスタンス化

5.5. カスタム拍生成ポートとロジックのイネーブル

5.6. FタイルPMA/FEC Direct PHYデザインのIPの接続

5.7. FタイルPMA/FEC Direct PHYデザインのシミュレーション

5.8. Fタイル・インターフェイスのプランニング

インテルのみ表示可能 — GUID: xbg1615854170190

Ixiasoft

5.4. F-Tile Reference and System PLL Clocks Intel® FPGA IPのインスタンス化

Fタイル PMA/FEC Direct PHY のデザインでは、F-Tile Reference and System PLL Clocks Intel® FPGA IPが必要です。シミュレーションとコンパイルには、このIPをインスタンス化して接続する必要があります。

このデザインでは、F-Tile Reference and System PLL Clocks Intel® FPGA IPに以下が必要です。

- 1つのシステムPLLに対するシステムPLLのモードとリファレンス・クロック・ソース。これは、データパスのクロックになります。

- FGT PMAのリファレンス・クロック・ソース。システムPLLとFGT PMAのリファレンス・クロック・ソースは、共有または個別にします。この例では、リファレンス・クロックを共有します。

1つのシステムPLLに対するシステムPLLのモードとリファレンス・クロック・ソースを指定するには、次の手順に従います。

- IP Catalogの検索フィールドに f-tile Reference と入力し、Transceiver PHY にある F-Tile Reference and System PLL Clocks Intel® FPGA IP をダブルクリックします。

- System PLL #0 タブで、次のパラメーターを指定します。

表 106. System PLL #0 のオプション パラメーター パラメーター値 Mode of system PLL ETHERNET_FREQ_830_156 を選択します。これは、システムPLLの入力周波数を156.25Mhz、出力周波数を830.078125MHzにコンフィグレーションします (F-Tile PMA/FEC Direct PHY Intel® FPGA IPのシステムPLL周波数に一致する必要があります)。 Refclk source RefClk #0。システムPLLのリファレンス・クロック・ソースを選択します。 RefClk #0 for FGT PMA オンにします。 - RefClk で、次のオプションを指定します。

表 107. RefClkのオプション パラメーター パラメーター値 Enable RefClk #0 for FGT PMA オンにします。このリファレンス・クロックは、システムPLL #0とFGT PMAで共有されます。 RefClk source RefClk #0。156.25MHz (F-Tile PMA/FEC Direct PHY Intel® FPGA IPのリファレンス・クロック周波数と同じ)。

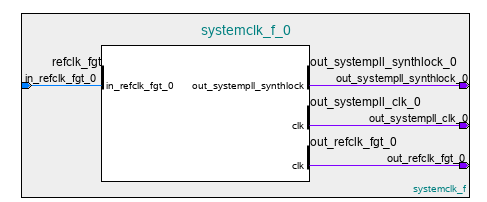

図 106. システムPLLとRefClkのオプション

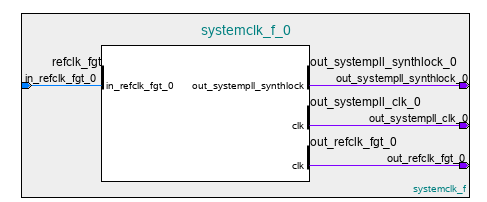

次の図は、この例におけるF-Tile Reference and System PLL Clocks Intel® FPGA IPのブロック記号と利用可能なポートを表しています。

図 107. F-Tile Reference and System PLL Clocks Intel® FPGA IP例のポート