インテルのみ表示可能 — GUID: uqt1523641783274

Ixiasoft

インテルのみ表示可能 — GUID: uqt1523641783274

Ixiasoft

1.6.1. SLD JTAG Bridge Index

インテル® Quartus® Prime開発ソフトウェアでは、パーティションとその子のSLD JTAGブリッジの複数のインスタンスをサポートしています。コンパイラーは、各インスタンスを区別するためにインデックス番号を割り当てます。ルート・パーティションのブリッジインデックスは、常に「None」です。

Signal Tapロジック・アナライザーをルート・パーティションに対してコンフィグレーションする場合は、Bridge Index値をJTAG Chain ConfigurationウィンドウでNoneに設定します。

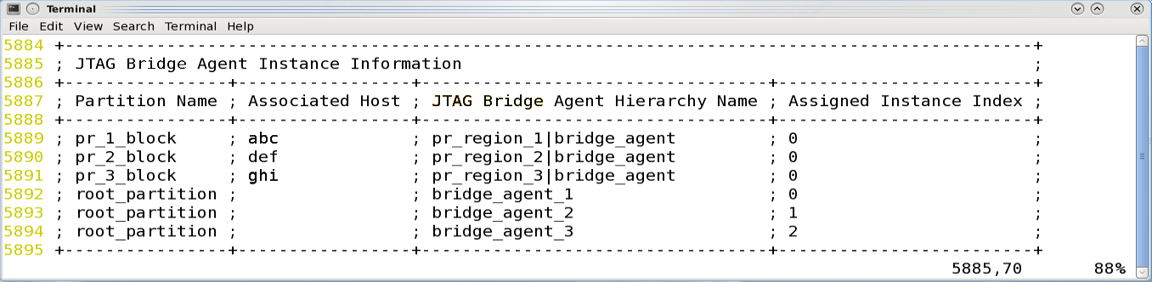

Compilation Reportのブリッジ・インデックス情報

デザイン合成後、Compilation Reportにデザイン内のSLD JTAG Bridge Agentのインデックス番号が一覧表示されます。Synthesis > In-System Debugging > JTAG Bridge Instance Agent Informationレポートを開くと、ブリッジ・インデックスの列挙方法の詳細が確認できます。レポートには、階層パスと関連インデックスが表示されます。

合成レポート ( <base revision>.syn.rpt ) では、この情報はJTAG Bridge Agent Instance Informationに表示されます。