インテルのみ表示可能 — GUID: mwh1410384983950

Ixiasoft

インテルのみ表示可能 — GUID: mwh1410384983950

Ixiasoft

6.6. デザイン例 : ダイナミックPLLリコンフィグレーション

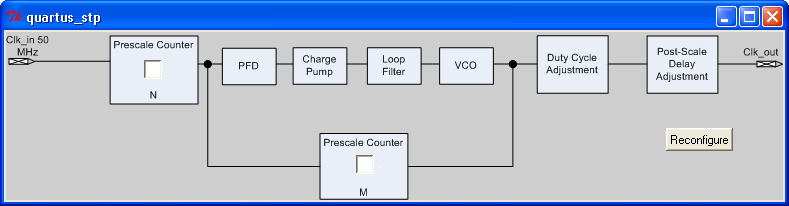

Stratix® PLLでは、実行時のPLL係数の動的更新が可能です。 Stratix® デバイスに内蔵された各エンハンストPLLに含まれるレジスターチェーンでは、プリスケール・カウンター (値mとn)、出力分周カウンター、および遅延カウンターの変更ができます。さらに、ALTPLL_RECONFIG IPコアに備えられた簡単なインターフェイスでは、このレジスターチェーンへのアクセスができます。また、ALTPLL_RECONFIG IPコアのキャッシュには、変更可能なPLLパラメーターがすべて含まれています。PLLパラメーターをすべてキャッシュ内で更新した後、ALTPLL_RECONFIG IP コアではPLLレジスターチェーンを駆動し、変更されたパラメーターでPLLを更新します。次の図で示す Stratix® のエンハンストPLLには、リコンフィグレーション可能な係数が含まれています。

このデザイン例の作成には、 Nios® II Development Kitの Stratix® Editionを使用しています。 sourceprobe_DE_dynamic_pll.zip ファイルには、このデザイン例の実行に必要なファイルが全て含まれており、次のファイルも含まれます。

- Readme.txt - テキストファイル。デザイン例に含まれるファイルを記述し、下図に示すTk GUIの実行方法を説明します。

- Interactive_Reconfig.qar - このデザイン例のためにアーカイブされた インテル® Quartus® Primeプロジェクトです。

図 86. TkおよびIn-System Sources and Probes Tcl Packageを使用して作成したインタラクティブPLLリコンフィグレーションGUI