インテルのみ表示可能 — GUID: mwh1410384625824

Ixiasoft

1. システム・デバッグ・ツールの概要

2. Signal Tapロジック・アナライザーを使用したデザインのデバッグ

3. Signal Probeを使用した迅速なデザイン検証

4. 外部ロジック・アナライザーを使用したインシステム・デバッグ

5. メモリーおよび定数のインシステム変更

6. In-System Sources and Probesを使用したデザインのデバッグ

7. System Consoleを使用したデザインの解析とデバッグ

8. トランシーバー・リンクのデバッグ

9. インテル® Quartus® Primeプロ・エディション ユーザーガイド: デバッグツールのアーカイブ

A. インテル® Quartus® Primeプロ・エディション ユーザーガイド

2.1. Signal Tapロジック・アナライザー

2.2. Signal Tapロジック・アナライザーのタスクフローの概要

2.3. Signal Tapロジック・アナライザーのコンフィグレーション

2.4. トリガーの定義

2.5. デザインのコンパイル

2.6. ターゲットデバイスのプログラム

2.7. Signal Tapロジック・アナライザーの実行

2.8. キャプチャしたデータの表示、解析、および使用

2.9. Signal Tapロジック・アナライザーを使用したパーシャル・リコンフィグレーション・デザインのデバッグ

2.10. Signal Tapロジック・アナライザーを使用したブロックベースのデザインのデバッグ

2.11. その他の機能

2.12. デザイン例 : Signal Tapロジック・アナライザーの使用

2.13. カスタム・トリガー・フローのアプリケーション例

2.14. Signal Tapスクリプティングのサポート

2.15. Signal Tapロジック・アナライザーを使用したデザインのデバッグ 改訂履歴

5.1. ISMCEをサポートするIPコア

5.2. In-System Memory Content Editorを使用したデバッグフロー

5.3. デザイン内インスタンスのランタイム修正のイネーブル

5.4. In-System Memory Content Editorを使用したデバイスのプログラミング

5.5. メモリー・インスタンスのISMCEへのロード

5.6. メモリー内のロケーションのモニタリング

5.7. Hex Editorを使用したメモリー内容の編集

5.8. メモリーファイルのインポートおよびエクスポート

5.9. 複数のデバイスへのアクセス

5.10. スクリプティング・サポート

5.11. メモリーおよび定数のインシステム変更 改訂履歴

7.1. System Consoleの概要

7.2. System Consoleのデバッグフロー

7.3. System Consoleと相互作用するIPコア

7.4. System Consoleの起動

7.5. System ConsoleのGUI

7.6. System Consoleのコマンド

7.7. コマンドライン・モードでのSystem Consoleの実行

7.8. System Consoleサービス

7.9. System Consoleの例とチュートリアル

7.10. On-Board インテル® FPGAダウンロード・ケーブルIIのサポート

7.11. システム検証フローにおけるMATLAB*とSimulink*

7.12. 廃止予定のコマンド

7.13. System Consoleを使用したデザインの解析とデバッグ 改訂履歴

8.1. デバイスのサポート

8.2. Channel Manager

8.3. トランシーバー・デバッグ・フローの手順

8.4. トランシーバーをデバッグ可能にするためのデザイン変更

8.5. インテルFPGAにデザインをプログラムする

8.6. Transceiver Toolkitへのデザインのロード

8.7. ハードウェア・リソースのリンク

8.8. トランシーバー・チャネルの特定

8.9. トランシーバー・リンクの作成

8.10. リンクテストの実行

8.11. PMAアナログ設定の制御

8.12. ユーザー・インターフェイス設定リファレンス

8.13. 一般的なエラーのトラブルシューティング

8.14. APIリファレンスのスクリプティング

8.15. トランシーバー・リンクのデバッグ 改訂履歴

インテルのみ表示可能 — GUID: mwh1410384625824

Ixiasoft

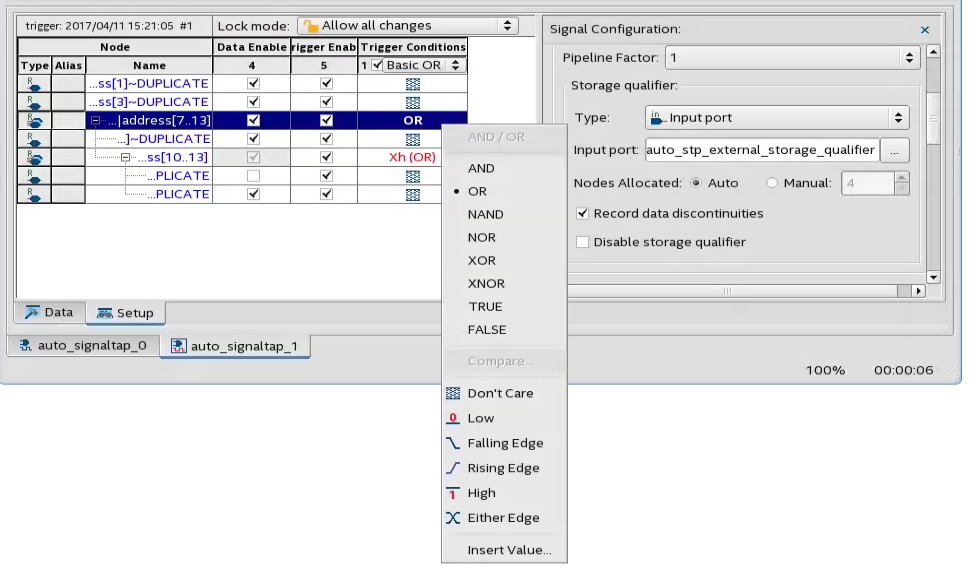

2.4.1.1. ネストされたグループによるBasic ORトリガー条件の使用

信号セットの指定をネストされたグループ (グループのグループ) として行う場合、Basic ORトリガータイプを使用すると、Signal Tapロジック・アナライザーによってAdvancedトリガー条件が生成されます。この条件によりグループ内の信号の並び替えが行われるため、デザインを再コンパイルする必要性が最小限に抑えられます。 ノードの親子関係が一定に保たれている限り、Advancedトリガー条件は変更されません。ノードの兄弟関係の変更は可能で、その際、デザインの再コンパイルは不要です。

ネストされたトリガー条件の評価優先順位の開始は、リーフグループを持つ最下位レベルからです。ロジック・アナライザーでは、結果として得られる論理値を使用して、親グループの論理値を計算します。グループの値を手動で設定する場合、グループメンバーの論理値による影響は、グループトリガーの結果に対してはありません。ネストされたトリガー条件を作成するには次を実行します。

- Trigger ConditionsでBasic ORを選択します。

- Setupタブでノードをいくつか選択します。複数のグループを選択に含めます。

- Setupタブを右クリックして、Groupを選択します。

- ネストされたグループを選択し、右クリックして、グループトリガー条件を設定します。この条件は、Reduction AND、OR、NAND、NOR、XOR、XNOR、あるいは論理TRUEまたはFALSEに適用されます。

注: ORおよびANDグループトリガー条件のみを、下位レベルのグループ (子としてのグループを持たないグループ) に対して選択します。図 30. ネストされたグループへのトリガー条件の適用