インテルのみ表示可能 — GUID: mwy1621361123580

Ixiasoft

インテルのみ表示可能 — GUID: mwy1621361123580

Ixiasoft

3.3.4.2.1. QDR-IV読み出しキャリブレーション

DQSenキャリブレーション

キャリブレーション・アルゴリズムでは、ハードウェアのステートマシンを使用しません。代わりに、ソフトウェアを使用してサイクルレベルの遅延をキャリブレーションし、DQSトラッキング・ハードウェアを使用してサブサイクルの遅延をキャリブレーションします。このアルゴリズムはメモリー内の適切なデータを必要とするため、保証されている書き込みに依存します。アルゴリズムはDQSトラッキングを有効にし、DQSイネーブルの位相コンポーネントをキャリブレーションします。その後保証された書き込みを発行し、連続読み出しを行います。アルゴリズムは、読み出し動作が成功するまでDQSenの値をサイクルごとにスイープします。DQSenキャリブレーションは読み出しのスキュー調整前に行われるため、合格を登録するには1つの成功したDQビットのみが必要です。アルゴリズムは、読み出しDQバスを動かし、少なくとも1つのDQビットが有効な読み出しウィンドウ内に収まるようにします。このプロセスは、他の読み出しグループすべてで繰り返されます。

デスキュー・キャリブレーション

読み出しのデスキュー・キャリブレーションは、書き込みレベリング前に行われます。また、少なくとも2回実行する必要があります (保証された書き込みからの単純なデータパターンを使用して書き込みのキャリブレーション前に1回、複雑なデータパターンを使用して書き込みのキャリブレーション後に1回)。

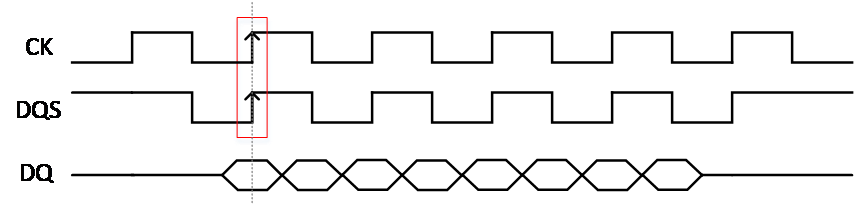

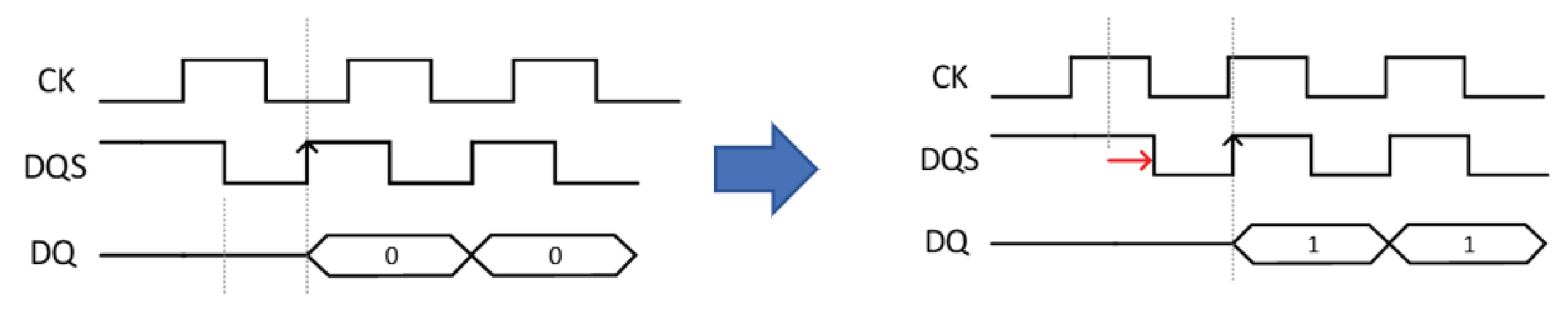

保証された書き込みを正しく機能させるために、保証された書き込みの前に書き込みレベリング・フェーズのトレーニングが行われます。書き込みレベリング・フェーズ・トレーニングの目的は、書き込みDQSの立ち上がりエッジをDRAMでMEM_CLKの立ち上がりエッジに揃えることです。

このアルゴリズムは、書き込みレベリング・フェーズ・トレーニングにDRAMの書き込みレベリング機能を使用します。このモードでは、次の動作が発生します。

- アルゴリズムは、書き込みDQS信号をトグルしながら、DQS出力遅延を (FPGA側で) 調整します。

- DRAMは、書き込みDQSの立ち上がりエッジを使用してMEM_CLKをサンプリングし、サンプリングした値をDQピンに出力します。

- アルゴリズムは、write_DQS信号をトグルしながらDQS出力を調整します。これは、DQピンで0から1への遷移が検出されるまで続きます。

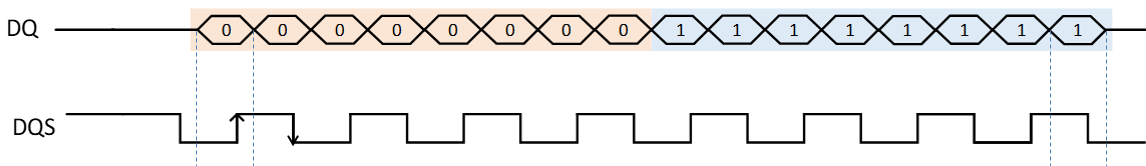

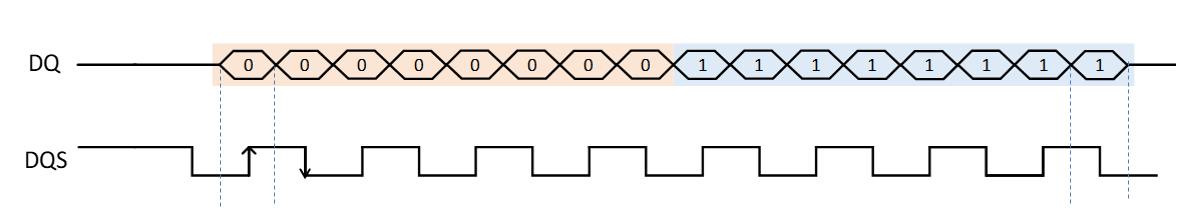

保証された書き込みでは、アルゴリズムは0のバーストを1つの位置に書き込み、1のバーストを別の位置に書き込みます。この2つの位置からの連続読み出しで取得するデータは、読み出しデスキュー・キャリブレーションの単純なデータパターンとして使用されます。

書き込みキャリブレーションの前に、デスキュー・キャリブレーション・アルゴリズムは保証された書き込みを実行し、dqs_inの遅延値を低から高にスイープすることで、読み出しウィンドウの右のエッジを見つけます。次に、アルゴリズムはdq_inの遅延値を低から高にスイープし、読み出しウィンドウの左のエッジを見つけます。その後、アルゴリズムは更新されたdqs_inおよびdq_inの遅延値を適用し、読み出しウィンドウを中央に配置します。このプロセスは、すべてのデータピンで繰り返されます。

書き込みパスがキャリブレーションされたら、アルゴリズムは複雑なデータパターンを使用して別の読み出しデスキュー・キャリブレーションを実行します。

Vref-inキャリブレーション

読み出しのVref-Inキャリブレーションは、Vref-Inを任意の値でプログラミングすることから始まります。次にアルゴリズムは、Vref-Inの値を開始値から両端までスイープし、それぞれの値の読み出しウィンドウを測定します。アルゴリズムは、最大の読み出しウィンドウを提供するVref-Inの値を選択します。Vref-Inは、DQ/DQS信号に使用されるI/OバンクのVCCIOから生成され、FPGAで内部的にキャリブレーションされます。

LFIFOキャリブレーション

読み出しのLFIFOキャリブレーションは、グループ間の読み出し遅延を正規化します。PHYでは、すべてのデータを単一のデータバスとしてコントローラーに提供する必要があります。LFIFOのレイテンシーは、最も遅い読み出しデータグループに対して、また、FIFO間の適切な同期に対応できるように十分な大きさである必要があります。