インテルのみ表示可能 — GUID: wnd1572970651244

Ixiasoft

1. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPについて

2. インテル® Agilex™ FPGA EMIF IP – 概要

3. インテル® Agilex™ FPGA EMIF IP - 製品アーキテクチャー

4. インテル® Agilex™ FPGA EMIF IP - エンドユーザーの信号

5. インテル® Agilex™ FPGA EMIF IP - メモリーIPのシミュレーション

6. インテル® Agilex™ FPGA EMIF IP – DDR4のサポート

7. インテル® Agilex™ FPGA EMIF IP - QDR-IVのサポート

8. インテル® Agilex™ FPGA EMIF IP – タイミング・クロージャー

9. インテル® Agilex™ FPGA EMIF IP – I/Oのタイミング・クロージャー

10. インテル® Agilex™ FPGA EMIF IP – コントローラーの最適化

11. インテル® Agilex™ FPGA EMIF IP – デバッグ

12. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPユーザーガイド・アーカイブ

13. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPユーザーガイドの改訂履歴

3.1.1. インテル® Agilex™ EMIFのアーキテクチャー: I/Oサブシステム

3.1.2. インテル® Agilex™ EMIFのアーキテクチャー: I/O SSM

3.1.3. インテル® Agilex™ EMIFのアーキテクチャー: I/Oバンク

3.1.4. インテル® Agilex™ EMIFのアーキテクチャー: I/Oレーン

3.1.5. インテル® Agilex™ EMIFのアーキテクチャー: 入力DQSクロックツリー

3.1.6. インテル® Agilex™ EMIFのアーキテクチャー: PHYクロックツリー

3.1.7. インテル® Agilex™ EMIFのアーキテクチャー: PLLリファレンス・クロック・ネットワーク

3.1.8. インテル® Agilex™ EMIFのアーキテクチャー: クロックの位相アライメント

3.3.4.3.1. キャリブレーション・レポートの情報を使用してのキャリブレーション・エラーのデバッグ

3.3.4.3.2. アドレスおよびコマンドのレベリング・キャリブレーション・エラーのデバッグ

3.3.4.3.3. アドレスおよびコマンドのデスキューエラーのデバッグ

3.3.4.3.4. DQSイネーブルエラーのデバッグ

3.3.4.3.5. 読み出しのデスキュー・キャリブレーション・エラーのデバッグ

3.3.4.3.6. VREFINキャリブレーション・エラーのデバッグ

3.3.4.3.7. LFIFOキャリブレーション・エラーのデバッグ

3.3.4.3.8. 書き込みレベリングエラーのデバッグ

3.3.4.3.9. 書き込みのデスキュー・キャリブレーション・エラーのデバッグ

3.3.4.3.10. VREFOUTキャリブレーション・エラーのデバッグ

4.1.1.1. DDR4のlocal_reset_req

4.1.1.2. DDR4のlocal_reset_status

4.1.1.3. DDR4のpll_ref_clk

4.1.1.4. DDR4のpll_locked

4.1.1.5. DDR4のac_parity_err

4.1.1.6. DDR4のoct

4.1.1.7. DDR4のmem

4.1.1.8. DDR4のstatus

4.1.1.9. DDR4のafi_reset_n

4.1.1.10. DDR4のafi_clk

4.1.1.11. DDR4のafi_half_clk

4.1.1.12. DDR4のafi

4.1.1.13. DDR4のemif_usr_reset_n

4.1.1.14. DDR4のemif_usr_clk

4.1.1.15. DDR4のctrl_amm

4.1.1.16. DDR4のctrl_amm_aux

4.1.1.17. DDR4のctrl_auto_precharge

4.1.1.18. DDR4のctrl_user_priority

4.1.1.19. DDR4のctrl_ecc_user_interrupt

4.1.1.20. DDR4のctrl_ecc_readdataerror

4.1.1.21. DDR4のctrl_ecc_status

4.1.1.22. DDR4のctrl_mmr_slave

4.1.1.23. DDR4のhps_emif

4.1.1.24. DDR4のemif_calbus

4.1.1.25. DDR4のemif_calbus_clk

4.1.2.1. QDR-IVのlocal_reset_req

4.1.2.2. QDR-IVのlocal_reset_status

4.1.2.3. QDR-IVのpll_ref_clk

4.1.2.4. QDR-IVのpll_locked

4.1.2.5. QDR-IVのoct

4.1.2.6. QDR-IVのmem

4.1.2.7. QDR-IVのstatus

4.1.2.8. QDR-IVのafi_reset_n

4.1.2.9. QDR-IVのafi_clk

4.1.2.10. QDR-IVのafi_half_clk

4.1.2.11. QDR-IVのafi

4.1.2.12. QDR-IVのemif_usr_reset_n

4.1.2.13. QDR-IVのemif_usr_clk

4.1.2.14. QDR-IVのctrl_amm

4.1.2.15. QDR-IVのemif_calbus

4.1.2.16. QDR-IVのemif_calbus_clk

4.4.1. ctrlcfg0

4.4.2. ctrlcfg1

4.4.3. dramtiming0

4.4.4. sbcfg1

4.4.5. caltiming0

4.4.6. caltiming1

4.4.7. caltiming2

4.4.8. caltiming3

4.4.9. caltiming4

4.4.10. caltiming9

4.4.11. dramaddrw

4.4.12. sideband0

4.4.13. sideband1

4.4.14. sideband4

4.4.15. sideband6

4.4.16. sideband7

4.4.17. sideband9

4.4.18. sideband11

4.4.19. sideband12

4.4.20. sideband13

4.4.21. sideband14

4.4.22. dramsts

4.4.23. niosreserve0

4.4.24. niosreserve1

4.4.25. sideband16

4.4.26. ecc3: ECCエラーおよび割り込みのコンフィグレーション

4.4.27. ecc4: ステータスとエラー情報

4.4.28. ecc5: 最新のSBEまたはDBEのアドレス

4.4.29. ecc6: 最新のドロップされた訂正コマンドのアドレス

4.4.30. ecc7: 最新のSBEまたはDBEのアドレスの拡張

4.4.31. ecc8: 最新のドロップされた訂正コマンドのアドレスの拡張

6.1.1. インテルAgilex EMIF IPにおけるDDR4のパラメーター: General

6.1.2. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Memory

6.1.3. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Mem I/O

6.1.4. インテルAgilex EMIF IPにおけるDDR4のパラメーター: FPGA I/O

6.1.5. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Mem Timing

6.1.6. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Controller

6.1.7. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Diagnostics

6.1.8. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Example Designs

7.1.1. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: General

7.1.2. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Memory

7.1.3. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: FPGA I/O

7.1.4. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Mem Timing

7.1.5. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Controller

7.1.6. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Diagnostics

7.1.7. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Example Designs

11.1. インターフェイスのコンフィグレーションにおける性能の問題

11.2. 機能的な問題の評価

11.3. タイミング問題の特徴

11.4. Signal Tapロジック・アナライザーでのメモリーIPの検証

11.5. ハードウェアのデバッグ・ガイドライン

11.6. ハードウェアの問題の分類

11.7. 外部メモリー・インターフェイス・デバッグ・ツールキットを使用したデバッグ

11.8. デフォルトのトラフィック・ジェネレーターの使用

11.9. コンフィグレーション可能なトラフィック・ジェネレーター (TG2) の使用

11.10. EMIFオンチップ・デバッグ・ポート

11.11. Efficiency Monitor

11.7.4.3.1. キャリブレーション・レポートの情報を使用してのキャリブレーション・エラーのデバッグ

11.7.4.3.2. アドレスおよびコマンドのレベリング・キャリブレーション・エラーのデバッグ

11.7.4.3.3. アドレスおよびコマンドのデスキューエラーのデバッグ

11.7.4.3.4. DQSイネーブルエラーのデバッグ

11.7.4.3.5. 読み出しのデスキュー・キャリブレーション・エラーのデバッグ

11.7.4.3.6. VREFINキャリブレーション・エラーのデバッグ

11.7.4.3.7. LFIFOキャリブレーション・エラーのデバッグ

11.7.4.3.8. 書き込みレベリングエラーのデバッグ

11.7.4.3.9. 書き込みのデスキュー・キャリブレーション・エラーのデバッグ

11.7.4.3.10. VREFOUTキャリブレーション・エラーのデバッグ

インテルのみ表示可能 — GUID: wnd1572970651244

Ixiasoft

11.7.4.8. ISSPタブ

ISSPタブでは、デザインのIn-System Sources and Probesのプローブデータを読み取り、ソース値を設定することができます。

デザインのISSPからプローブデータを再度読み込むには、In-System Probesセクションを展開し、Update Probe Infoボタンをクリックします。

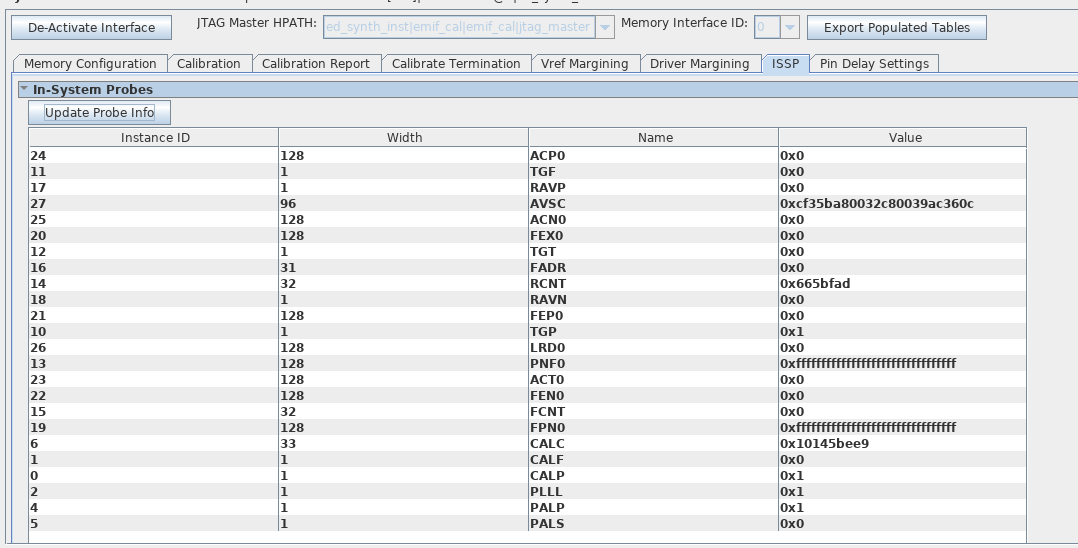

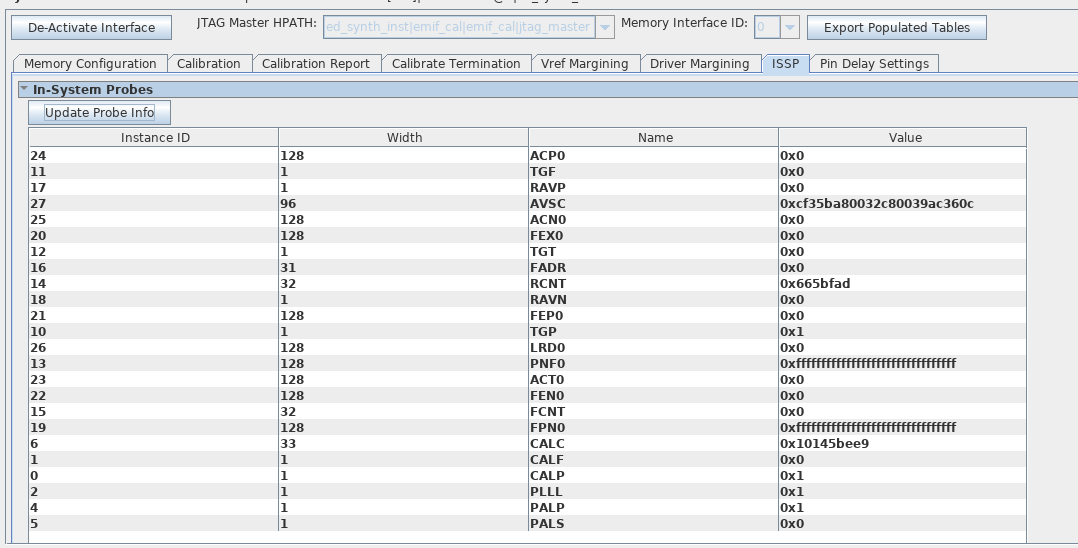

図 186. 表示されるプローブデータ

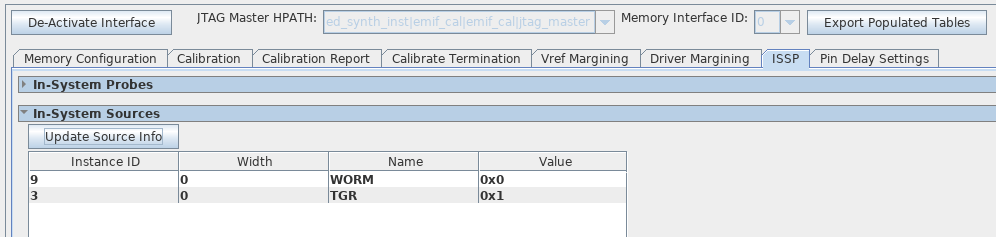

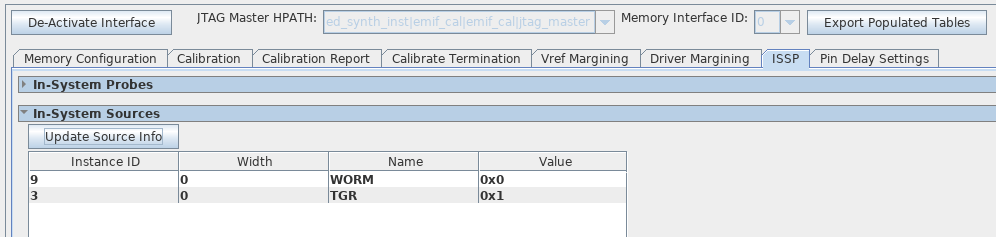

デザインのISSPからソースデータを再度読み込むには、In-System Sourcesセクションを展開し、Update Source Infoボタンをクリックします。

図 187. 表示されるソースデータ

ソースデータを上書きするには、Instance Nameを選択し、Writedataの値を変更します。新しいソース値は、Write Source Infoをクリックすると書き込まれます。

EMIFデザイン例のISSPの説明

| インスタンス名 | 詳細 |

|---|---|

| PLLL | PLLロック信号。値1はPLLがロックされていることを意味し、値0はPLLがリファレンス・クロックにロックできないことを意味します。 |

| RCNT | 読み出しデータの総数。 |

| FCNT | 合計失敗数 (データの不一致数)。 |

| FADR | データの不一致が報告された最初のアドレス。 |

| RAVP | 最初に失敗したアドレスの前のデータからの有効な読み出しデータ。 |

| RAVN | 最初に失敗したアドレスの後のデータからの有効な読み出しデータ。 |

| PNF# | 永続的なPass Not Failフラグ。1は合格、0は不合格を示します。 |

| FPN# | 最初のデータの不一致に対するPNFフラグ。 |

| FEX# | 最初に失敗した読み出しの想定読み出しデータ。 |

| FEP# | 最初に失敗した読み出しの前の想定読み出しデータ。 |

| FEN# | 最初に失敗した読み出しの後の想定読み出しデータ。 |

| ACT# | 最初に失敗した読み出しの実際の読み出しデータ。 |

| ACP# | 最初に失敗した読み出しの前の実際の読み出しデータ。 |

| ACN# | 最初に失敗した読み出しの後の実際の読み出しデータ。 |

| LRD# | 繰り返された読み出しの結果。エラーが発生すると、ドライバーは最初に失敗したアドレスから再度読み出しを行います。これは、繰り返される読み出しのPNFフラグです。 |

| AVSC | Avalon Stall Count - 連続する次の3つの32ビット信号 (MSBからLSB)

|

| PALP | クロック位相アライメント・ロック・ステータス。 |

| PALS | クロック位相アライメント・ロック (二次)。

注: これはAgilex FPGAでは使用されません。

|

| CALC | キャリブレーション・カウンター。最上位ビットはdone信号です。値1はキャリブレーションが完了していることを意味し、値0はキャリブレーションが進行中であることを意味します。他の32ビットはクロックカウンターで、キャリブレーション中に経過したクロック数を追跡します。 |

| TGP | トラフィック・ジェネレーターのPassフラグ。合格 = 1。 |

| TGF | トラフィック・ジェネレーターのFailフラグ。失敗 = 1。 |

| TGT | トラフィック・ジェネレーターのタイムアウト。タイムアウト = 1。 |

| TGR | トラフィック・ジェネレーターのリセット。アクティブHigh。TGRをトグルし、トラフィック・ジェネレーターを再実行します。 |

| RSTN | デザイン例のグローバルリセット。アクティブLow。RSTNをトグルし、インターフェイスをリセットおよび再キャリブレーションします。 |

| WORM | 1に設定すると、WORMモードが有効になります。WORMモードでは、データの不一致が発生した場合、システムは可能な限り多くのトラフィックを停止し、同じアドレスに読み出しを発行します。このモードでは、最初のデータの不一致で実行が停止するため、永続的なPNFは意味がなくなります。デフォルトで、WORMモードはオフになっています。 |

| PRTY | DDR4メモリーのパリティーステータスを示します。値0はエラーがないことを示し、値1はエラーを示します。デザインがDDR4ではない場合、もしくはAC Parity Latencyパラメーターがパラメーター・エディターで無効になっている場合は、この値は更新されません。 |