インテルのみ表示可能 — GUID: uon1547134061436

Ixiasoft

インテルのみ表示可能 — GUID: uon1547134061436

Ixiasoft

10.4.3. バンク・インターリーブ

- ページサイズとは、単一のアクティブ化コマンドでアクセスする任意の行の列位置の最小数を指しています。

- DDR4の場合、バンクはバンクアドレスとバンクグループを指しています。

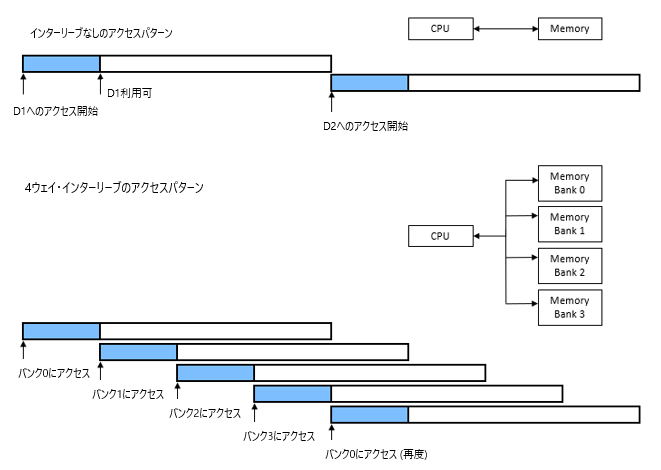

インターリーブを使用しない場合、コントローラーは、アドレスをSDRAMデバイスに送信し、要求されたデータを受信後、SDRAMデバイスでプリチャージおよび再アクティブ化が行われるのを待機してから次のデータ・トランザクションを開始します。そのため、数クロックサイクルが浪費されます。

インターリーブにより、SDRAMデバイスのバンクでは、バックグラウンドの動作とアクセスサイクルを交互に行うことができます。1つのバンクでプリチャージとアクティブ化サイクルを実行している間に、別のバンクがアクセスされます。バンクを交互に切り替え、各バンクのプリチャージとアクティブ化の時間をマスクすることにより、コントローラーのパフォーマンスを向上させます。システムに4つのバンクがある場合、コントローラーは1つのデータ要求をそれぞれのバンクに連続したクロックサイクルで理想的に送信することができます。

例えば、最初のクロックサイクルでCPUはバンク0にアドレスを送信し、2番目のクロックサイクルで次のアドレスをバンク1に送信します。その後、3番目と4番目のクロックサイクルで、3番目と4番目のアドレスをバンク2と3にそれぞれ送信します。シーケンスは次のとおりです。

- コントローラーはアドレス0をバンク0に送信します。

- コントローラーはアドレス1をバンク1に送信し、データ0をバンク0から受信します。

- コントローラーはアドレス2をバンク2に送信し、データ1をバンク1から受信します。

- コントローラーはアドレス3をバンク3に送信し、データ2をバンク2から受信します。

- コントローラーはデータ3をバンク3から受信します。

次の図は、インターリーブを使用して帯域幅を拡大する方法を示しています。

コントローラーは、3つのインターリーブ・オプションをサポートしています。

CS-BG-Bank-CID-Row-Col - これは、インターリーブを行わないオプションです。このオプションを選択し、ランダムなトラフィックでの効率を改善します。

CS-CID-Row-Col-Bank-BG - このオプションでは、チップセレクト・インターリーブなしのバンク・インターリーブを使用します。このオプションを選択し、小さなデータ構造をチップ内のすべてのバンクに分散することで、連続するトラフィックの効率を向上させます。

CID-Row-CS-Bank-Col-BG - このオプションでは、チップセレクト・インターリーブありのバンク・インターリーブを使用します。このオプションを選択し、連続するトラフィックと複数のチップセレクトの効率を向上させます。このオプションでは、小さなデータ構造を複数のバンクおよびチップに分散させることができます。

バンク・インターリーブは固定パターンのデータ・トランザクションであり、ベストケースの帯域幅とレイテンシーの実現を可能にします。また、開いているバンク間での十分なインターリーブ・トランザクションを可能にすることで、tRCを完全に隠します。最適なシステムでは、バンク・インターリーブ・トランザクションの100%の効率を8つのバンクで達成することができます。バンクが8つ未満のシステムで100%を達成することはほとんどありません。