インテルのみ表示可能 — GUID: ltk1621270941522

Ixiasoft

インテルのみ表示可能 — GUID: ltk1621270941522

Ixiasoft

3.3.4.1. DDR4のキャリブレーション・アルゴリズム

レベリング・キャリブレーション

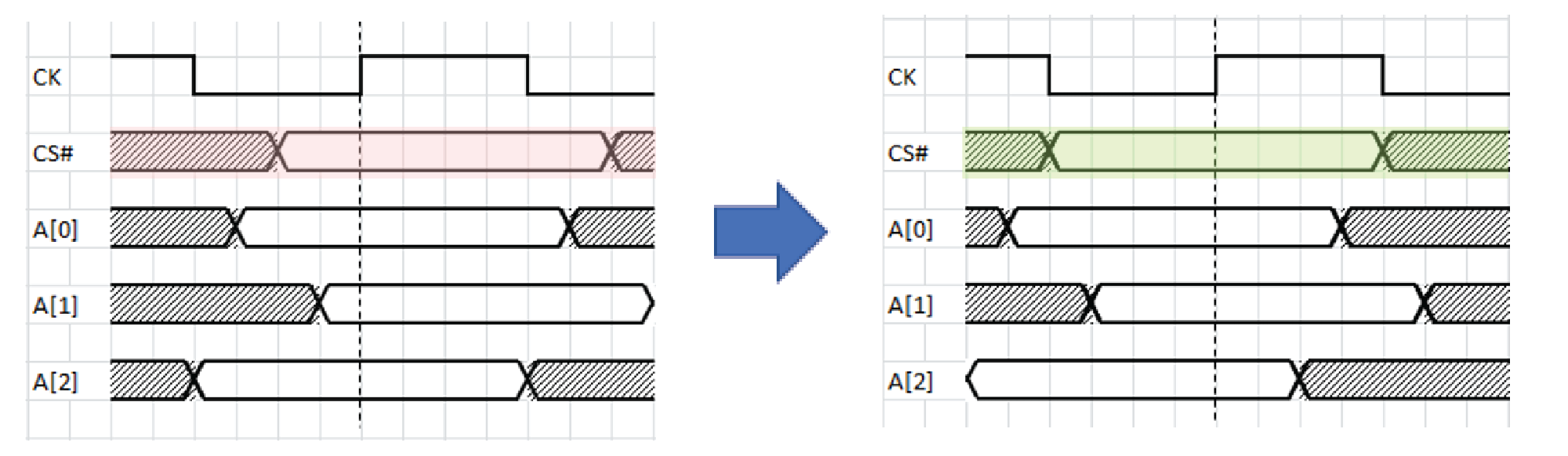

FPGAは、他のアドレスおよびコマンド信号を一定に保ちながら、CS#およびCAS#/A15信号をトグルして読み出しコマンドをメモリーに送信し、DQS信号がトグルするかを監視します。DQS信号がトグルすると、読み出しコマンドが受け入れられたことを示しています。アルゴリズムはその後、さまざまな遅延値を使用して繰り返し、最適なウィンドウを探します。このステージでは、アドレスおよびコマンドバス全体とCS#を動かします。

デスキュー・キャリブレーション

デスキュー・キャリブレーションでは、DDR4のアドレスおよびコマンドパリティー機能を使用します。これらのピンをデザインから省略しないでください。デスキュー・キャリブレーションでは、ODTピンおよびCKEピンのスキューを調整することができません。これらの信号は、アドレスおよびコマンドパリティーの計算に含まれていません。

デスキュー・キャリブレーション・テストは、2つのループで構成されます。最初のループでは、FPGAはアドレスおよびコマンドピンの遅延を調整し、アドレス・パリティー・ビットを送信します。DDR4メモリーデバイスは、パリティー・ビットを検出するとアラート信号で応答します。テストでは、ODT信号とCKE信号以外のすべてのアドレスおよびコマンド信号でこのプロセスが繰り返されます。最初のループでは、同じランク内に複数のコンポーネントがある場合に、ウィンドウの結合を検出します。最適ではないボードレイアウトの場合、最初のループで検出されるウィンドウが1メモリー・クロック・サイクルよりも大きい場合があります。

2番目のループでは、アルゴリズムはパリティー挿入パターンを反転し、最初のループで検出されたウィンドウ内で遅延をスイープします。同じランクのすべてのメモリー・コンポーネントがコマンドを正しく受信している場合、2番目のループでアラート信号はトグルしません。このチェックでは、ウィンドウの交差を検出し、アドレスとコマンドのスキュー調整の精度を向上させます。