インテルのみ表示可能 — GUID: vtw1583026410662

Ixiasoft

インテルのみ表示可能 — GUID: vtw1583026410662

Ixiasoft

7.4.2. リファレンス・スタックアップ

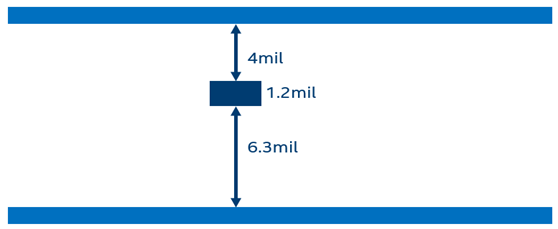

幅、厚さ、エッジからエッジの間隔などのトレースのジオメトリー、および基準面までの距離はすべて、トレース・インピーダンスとクロストークのレベルに影響を与えることを理解することが重要です。

| 層 | タイプ | 厚さ |

|---|---|---|

| SM TOP | 0.5 | |

| L1 | 信号 | 1.8 |

| D1 | プリプレグ | 2.7 |

| L2 | gnd/電源 | 1.2 |

| D2 | コア | 4.0 |

| L3 | 信号 | 1.2 |

| D3 | プリプレグ | 6.3 |

| L4 | gnd/電源 | 1.2 |

| D4 | コア | 4.0 |

| L5 | 信号 | 1.2 |

| D5 | プリプレグ | 6.3 |

| L6 | gnd/電源 | 1.2 |

| D6 | コア | 4.0 |

| L7 | 信号 | 1.2 |

| D7 | プリプレグ | 6.3 |

| L8 | gnd | 1.2 |

| D8 | コア | 4 |

| 電源 | 1.2 | |

| プリプレグ | 6.3 | |

| 電源 | 1.2 | |

| コア | 4 | |

| gnd | 1.2 | |

| プリプレグ | 6.3 | |

| 電源 | 1.2 | |

| コア | 4 | |

| L9 | gnd | 1.2 |

| D9 | プリプレグ | 6.3 |

| L10 | 信号 | 1.2 |

| D10 | コア | 4.0 |

| L11 | gnd/電源 | 1.2 |

| D11 | プリプレグ | 6.3 |

| L12 | 信号 | 1.2 |

| D12 | コア | 4.0 |

| L13 | gnd/電源 | 1.2 |

| D13 | プリプレグ | 6.3 |

| L14 | 信号 | 1.2 |

| D14 | コア | 4.0 |

| L15 | gnd/電源 | 1.2 |

| D15 | プリプレグ | 2.7 |

| L16 | 信号 | 1.8 |

| SM BOT | 0.5 | |

| 合計 | 120.1 |

シミュレーションでは、リファレンス・スタックアップの高さは120ミルになるように選択され、最大の信号ビアのカップリング (110ミル) に対応します。同時に、EMIFのデザイン・ガイドラインが引用されます。 インテル® では、ボード設計者に対して、EMIFレイアウトのPCBデザインで、110ミルの信号ビアのカップリングを超えないようにすること (内層でのストリップライン配線) を推奨しています。

PCBのスタックアップの高さが120ミルを超える場合、 インテル® では、EMIF信号を上層に配線し、信号ビアのカップリングが110ミルを超えないようにすることを推奨しています。

上の図では、リファレンス・スタックアップの材料はFR4として選択されています。これは、設計段階のシミュレーションでワーストケースの信号損失を表すものです。損失が少ない材料の場合、エンドツーエンドの最大配線長は、デザイン・ガイドラインで推奨されているエンドツーエンドの配線長よりも長くなります。ただし、時間領域のチャネル・シミュレーションを実行し、タイミング要件が満たされていることを確認する必要があります。

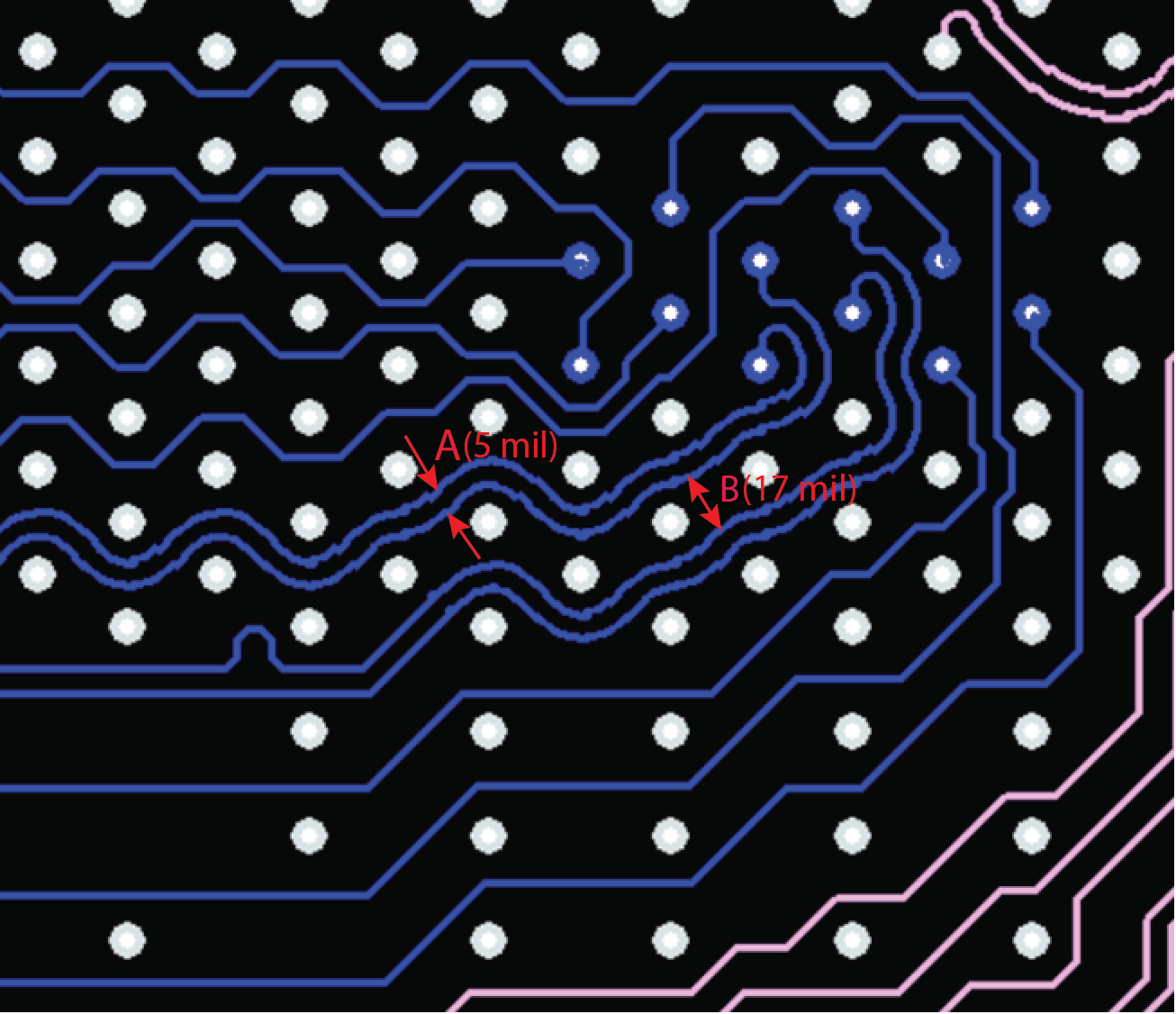

インテル® Agilex™ ファミリーのピンのフロアプランは、1mmピッチのHEXパターンです。次の図は、FPGAファンアウト領域内のPCBにおけるIO12 (1バイト・データ) の配線例を示しています。

次の一般的な注意事項は、QDR-IVトポロジーのEMIF配線ガイドラインに適用されます。

- 間隔に関する要件はすべて、EMIF配線ガイドラインの表に示されているPCBで満たす必要のある最小要件です。

- ガイドラインの表で、ブレークアウト (BO1/BO2) の間隔には2つの異なる値があります。最初の値は、ペアとして配線される2つの信号 (密結合の信号) 間の最小間隔を表しており、上の図ではA (5mil) としてマークされています。2番目の値は、2つのペア間の最小間隔を表し、上の図ではB (17mil) としてマークされています。

- メインルート (M) の間隔には、ミルでの値と式の両方があります。式内のhは、トレースから最も近い基準面までの高さまたは距離を表します。リファレンス・スタックアップとは異なるスタックアップを使用する場合、ボード設計者はこの式を使用して正しい間隔要件を計算する必要があります。

- CLKまたはQK/DKに差動インピーダンスのターゲットはありません。ボード設計者は、シングルエンドのインピーダンス・ターゲットに従い、ペア内の信号を3から4ミル間隔の密結合で維持する必要があります。QK/DKおよびCLK/CLKBに関しては、 QDR-IVのコンフィグレーションにおけるスキュー・マッチング・ガイドライン を参照してください。

- ガイドラインの表で、SLはストリップライン配線推奨を意味し、USは上層 (マイクロストリップ) 配線推奨を意味しています。

- ガイドラインの表のトレース幅の値/ジオメトリーは、リファレンス・スタックアップに基づくターゲット・インピーダンスに設計されたトレースを表しています。このトレース・ジオメトリーは、実際のスタックアップとガイドラインの表のターゲット・インピーダンスに基づき設計する必要があります。

- ガイドラインの表で、BO1およびBO2はファンアウト配線の長さを表しています。Mは、ファンアウト外 (PCBメイン) の配線長を表しています。