インテルのみ表示可能 — GUID: vds1598290349042

Ixiasoft

インテルのみ表示可能 — GUID: vds1598290349042

Ixiasoft

9.3.1. アドレス/コマンドのシミュレーション・デッキ

このコンフィグレーションには次の特徴があります。

- 12ピンのレーン内の2つのピンは、差動クロックパターンで駆動され、CK0とCK0_Nのクロックペアにマッピングされます。これらのピンは、反復するクロックパターンで駆動、位相調整されるため、CK0/CK0_Nの立ち上がりエッジまたは立ち下がりエッジが有効なデータウィンドウの中央になります。

- DDR4の場合、CK0/CK0_Nはレーン内のピン8/9にマッピングされます。

- QDR4の場合、CK0/CK0_Nはレーン内のピン4/5にマッピングされます。

- アドレス/コマンド・ピンのシンボルレートは、メモリー・テクノロジーの特性と一致します。

- DDR4では、アドレス/コマンド・チャネルはシングルデータレートです。

- QDR4では、アドレス/コマンド・チャネルはダブルデータレートです。

- 1つのピンが被害側のピンとして指定され、PRBS-10パターンで駆動されます (3回繰り返される)。

- DDR4では、ピン5が被害側のピンとして指定されます。

- QDR4では、ピン8が被害側のピンとして指定されます。

- 残りのピンは、同じ加害側のPRBS-15のデータパターンで駆動されます。

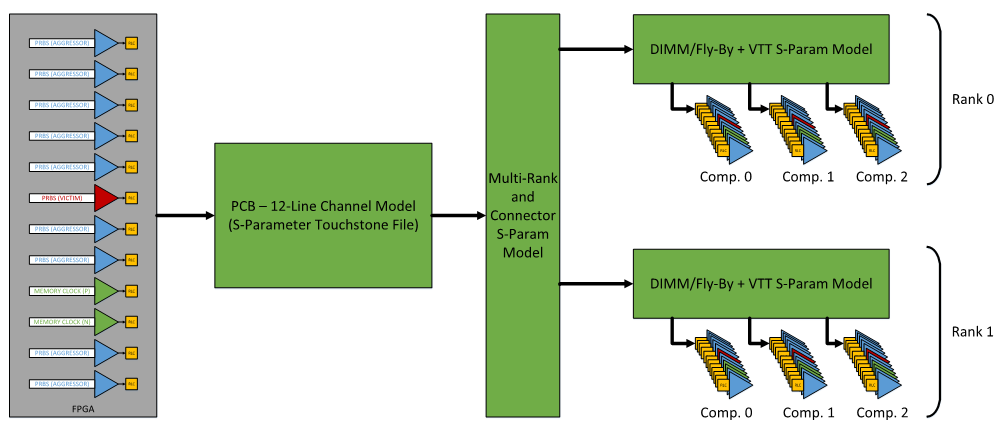

次の図は、アドレス/コマンド・シミュレーション・デッキの構造を表しています。

シミュレーション・デッキでは、12ラインのチャネルモデルを想定しています。各ブロックの目的については、以下のセクションで説明します。

FPGA

上の図の左端では、12個のFPGA IBISモデルがインスタンス化され、IPで指定されているメモリークロックとアドレス/コマンドの電気的設定に一致するようにコンフィグレーションされています。パターン・ジェネレーターはこのサブサーキット内に埋め込まれており、IPで生成されるパラメーター・ファイルを介して自動的にコンフィグレーションされます。

PCB - 12ラインのチャネルモデル

このブロックは、そのインターフェイスのアドレス/コマンド・バスのレーン0を実装する信号と一致する12ライン (24ポートとグランド) のチャネルモデルに接続します。デフォルトで、このサブサーキットは12本の独立した理想的な50オーム伝送ラインをインスタンス化します。これは、IPで生成されたパラメーター・ファイルで次のオプションを指定することで置き換えることができます。

| パラメーター名 | デフォルト値 | 詳細 |

|---|---|---|

| USE_AC_PCB_EXTRACTION | False | 24ポートのTouchstone抽出をアドレス/コマンドのシミュレーションで使用するかを指定します。Trueに設定している場合は、AC_PCB_EXTRACTION_FILEパラメーターで有効なTouchstoneファイルの位置を指定する必要があります。Falseに設定すると、理想的な伝送ラインモデルが使用されます。 |

| AC_PCB_EXTRACTION_FILE | <empty> | 24ポートのTouchstone抽出ファイルのファイル名を指定します (.s24p)。これは、アドレス/コマンド・チャネルを表すものです。最初の12ピンは、FPGAのボールに接続されるレーン0のピン0から11にマッピングされます。次の12ピンは、チャネルの遠いほうの端にマッピングされます。これは、メモリーボール (ポイントツーポイント直接接続の場合)、またはマルチランク・トポロジーの分岐点のいずれかです。 |

マルチランクおよびコネクターのモデル

次の内容を行う場合は、このブロックを使用します。

- インターフェイスのマルチランク・トポロジーをモデル化し、DIMMの間隔、チャネルのロード、コンポーネントのスタックなどのパラメーターの影響を検討する

- ベンダーより提供されているシミュレーション・モデルを挿入し、DIMMコネクターの影響をモデル化する

このブロックは、アドレス/コマンドPCB抽出モデルの終わりと各ランクのフライバイトポロジーの始まりの間にあります。抽出モデルを指定しない場合、ブロックのデフォルトモデルは次のようになります。

- シングルランクDDR4システムの場合、このブロックのデフォルトモデルはダイレクトパススルーです。

- デュアルランクDDR4システムの場合、このブロックのデフォルトモデルはランク0に直接接続します。また、12本の独立した50オーム、50ps伝送ラインをランク0とランク1の間に挿入し、2つのランク間のわずかな遅延差をモデル化します。

- クアッドランクDDR4システムの場合、このブロックのデフォルトモデルはランク0とランク1に直接接続します。また、12本の独立した50オーム、50ps伝送ラインをランク0/1とランク2/3の間に挿入します。

このデフォルトの動作は、独自のSパラメーター・モデルを指定することにより上書きすることができます。その場合は、次のオプションを使用します。モデルのポート数は、IPで計算されるシステム内のA/Cランク数であるMEMAC_RANKSと一致する必要があることに注意してください。値1、2、または4は、シングル、デュアル、またはクアッドランクのシステムに対応し、それぞれ24、36、または60ポートのモデルが必要です。

| パラメーター名 | デフォルト値 | 詳細 |

|---|---|---|

| USE_AC_MULTIRANK_CONNECTOR_EXTRACTION | False | NポートのTouchstone抽出をアドレス/コマンドのシミュレーションで使用し、マルチランク分岐トポロジーやDIMMコネクターをモデル化するかを指定します。Trueに設定されている場合は、AC_MULTIRANK_CONNECTOR_EXTRACTION_FILEパラメーターで有効なTouchstoneファイルの位置を指定する必要があります。Falseに設定すると、理想的な伝送ラインモデルが使用されます。 |

| AC_MULTIRANK_CONNECTOR_EXTRACTION_FILE | <empty> | NポートのTouchstone抽出ファイルのファイル名を指定します (.sNp)。これは、アドレス/コマンド・チャネルを表すものです。最初の12ピンは、12ラインのA/Cチャネルモデルのエンドポイントに接続されるレーン0のピン0から11にマッピングされます。次の12ピンは、ランク0のA/Cフライバイトポロジーの先頭に接続されます。MEMAC_RANKSが1より大きい場合、次の12ピンはランク1のアドレス/コマンド・フライバイ・トポロジーに接続されます。クアッドランク・システムでは、ランク2およびランク3に接続されます。 |

DIMM/フライバイ + VTTモデル

このブロックは、マルチコンポーネント・メモリー・インターフェイスのアドレス/コマンド・バスのフライバイトポロジーをモデル化します。このファイルを使用し、アドレス/コマンド・インターフェイスのシグナル・インテグリティーに影響を与える可能性のある次のような要因を調整することができます。

- コンポーネントのロード

- コンポーネントの間隔

- コンポーネント間のトレース・ジオメトリー/インピーダンス

- DDPコンポーネントを使用した場合と平面コンポーネントを使用した場合の影響

- 終端抵抗ネットワークの配置/値の影響

- シグナル・インテグリティーに対するトレース間隔の影響

- ビア、バックドリル、またはボードの両側におけるコンポーネントの配置の影響

デフォルトで、このブロックはフライバイチェーンのMEMAC_COMP_PER_RANKSコンポーネントを生成します。最初のコンポーネントは、サブサーキットの最初の12ポートに直接接続されます。後続のコンポーネントは、12本の独立した50オーム、50psの理想的な伝送ラインを使用して前のコンポーネントに接続されます。フライバイチェーンの最後のコンポーネントでは、各信号が50オームの抵抗を介してVTTソースに終端されます。差動クロックは、0.01uFのコンデンサーを介してVTTソースにAC結合されることに注意してください。

このデフォルトの動作は、独自のSパラメーター・モデルを指定することにより上書きすることができます。その場合は、次のオプションを使用します。モデルのポート数は、IPで計算されるシステム内のA/Cコンポーネント数であるMEMAC_COMP_PER_RANKSと一致する必要があることに注意してください。値が1の場合の最小ポート数は24ポートです。フライバイチェーン内のコンポーネントが追加されるたびに、12ポートずつ増加します。

| パラメーター名 | デフォルト値 | 詳細 |

|---|---|---|

| USE_AC_FLYBY_EXTRACTION | False | NポートのTouchstone抽出をアドレス/コマンドのシミュレーションで使用し、フライバイトポロジーをモデル化するかを指定します。Trueに設定されている場合は、AC_FLYBY_EXTRACTION_FILEパラメーターで有効なTouchstoneファイルの位置を指定する必要があります。Falseに設定すると、理想的な伝送ラインモデルが使用されます。 |

| AC_FLYBY_EXTRACTION_FILE | <empty> | NポートのTouchstone抽出ファイルのファイル名を指定します (.sNp)。これは、アドレス/コマンド・チャネルを表すものです。最初の12ピンは、12ラインのA/Cマルチランク/コネクター・モデルのエンドポイントに接続されるレーン0のピン0から11にマッピングされます。次の12ピンは、アドレス/コマンド・フライバイ・トポロジーの最初のコンポーネントに接続されます。MEMAC_COMP_PER_RANKSが1より大きい場合、次の12ピンはチェーン内の各追加コンポーネント (12ポートモデル、最大9コンポーネント) に接続されます。 |