インテルのみ表示可能 — GUID: ugf1547065728766

Ixiasoft

インテルのみ表示可能 — GUID: ugf1547065728766

Ixiasoft

3.5. インテル® Agilex™ EMIF IPにおけるユーザーが要求するリセット

| 詳細 | |

|---|---|

| リセットに関連する信号 | local_reset_req (入力) local_reset_done (出力) |

| ユーザーロジックでいつリセットを要求できるか | local_reset_reqは、local_reset_doneがHighになっている場合にのみ有効です。 デバイスの電源投入後に最初のキャリブレーションが完了すると、キャリブレーションが成功しているかいないかにかかわらず、local_reset_done信号はHighに遷移します。ユーザーモードでのその後のキャリブレーションでは、キャリブレーションが完了すると、local_reset_doneはHighに遷移します。デバイスの電源投入後の最初のキャリブレーションでは、local_reset_done信号がHighに遷移するまでにより多くの時間がかかります。これは、PHYを動作状態にする際に多くの操作が必要なためです。 |

| ユーザーが要求するリセットは必須要件か | ユーザーが要求するリセットはオプションです。I/O SSMは、デバイスの電源投入シーケンスの一部として、メモリー・インターフェイスが既知の状態から開始することを自動的に保証します。ユーザーが要求するリセットは、デバイスの電源投入シーケンス後にユーザーロジックでメモリー・インターフェイスを明示的にリセットする必要がある場合にのみ必要です。 |

| ユーザーが要求したリセットは実際にいつ発生するか | 各EMIF IPインスタンスには独自のローカルリセット要求ポートがあり、再キャリブレーションの際にはそれをアサートする必要があります。I/O SSMは、制御するすべてのEMIFインターフェイスのリセット要求を継続的にスキャンし、可能な場合はそれらを再キャリブレーションします。再キャリブレーションの正確なタイミングを予測することはできません。 |

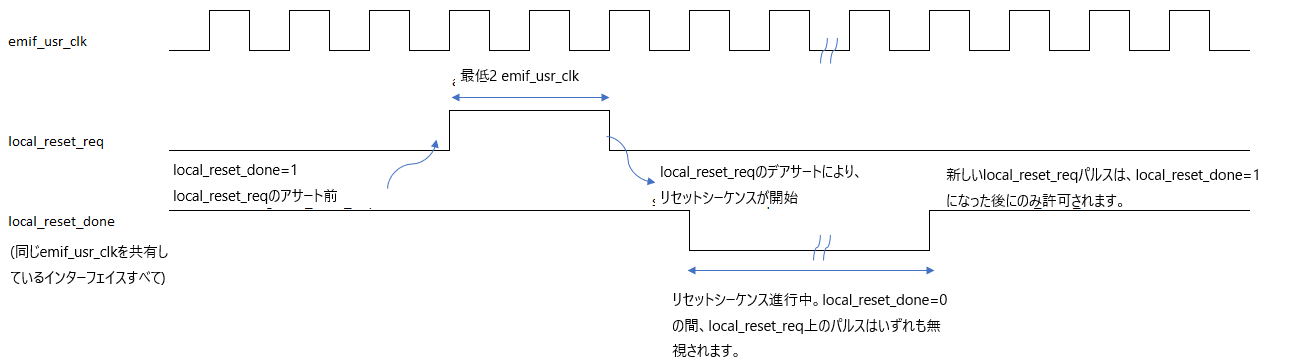

| タイミング要件とトリガーメカニズム | リセット要求は、local_reset_req信号をLowからHighに遷移させ、信号をHighの状態で少なくとも2 EMIFコア・クロック・サイクル間維持した後、信号をHighからLowに遷移させることで送信されます。local_reset_reqは、満たすべきセットアップまたはホールドのタイミングがないという点で非同期ですが、最小パルス幅要件である2 EMIFコア・クロック・サイクルを満たす必要があります。 |

| 外部メモリー・インターフェイスをリセット状態に維持できる期間 | 外部メモリー・インターフェイスを無期限にリセット状態で維持することはできません。local_reset_reqを継続してHighにアサートしても効果はありません。リセット要求は、完全な0->1->0パルスで完了します。 |

| 初期キャリブレーションの延期 | 初期のキャリブレーションを省略することはできません。local_reset_done信号は、初期のキャリブレーション完了後にのみHighに駆動されます。 |

| リセット範囲 (外部メモリー・インターフェイス内) | EMIFをパワーアップ状態に戻すために必要な回路のみがリセットされます。リセットシーケンスから除外されるのは、IOSSM、IOPLL、DLL、およびCPAです。 |

| リセット範囲 (I/O行内) | local_reset_reqは、インターフェイスごとのリセットです。 |

ユーザーが要求するリセットの開始方法

ステップ1 - 前提条件

local_reset_reqをアサートする前に、ユーザーロジックではlocal_reset_done信号がHighになっていることを確認する必要があります。

デバイスの電源投入シーケンスの一部として、インターフェイスのキャリブレーション・シーケンスが完了すると、キャリブレーションが成功しているかいないかにかかわらず、local_reset_done信号が自動的にHighに遷移します。

ステップ2 - リセット要求

前提条件が満たされると、ユーザーロジックでは、local_cal_req信号をLowからHighに駆動し、Lowに再度戻す (つまり、パルス1を送信する) ことでリセット要求を送信することができます。

- LowからHighおよびHighからLowへの遷移は非同期で発生させることができます。すなわち、クロックエッジに関連して発生する必要はありません。ただし、パルスは最低2 EMIFコア・クロック・サイクルの最小パルス幅を満たしている必要があります。例えば、emif_usr_clkの周期が4nsの場合、local_reset_reqパルスは少なくとも8ns (emif_usr_clkで2周期) 維持する必要があります。

- リセット要求は、HighからLowへ遷移した後にのみ完了したとみなされます。EMIF IPは、local_reset_reqが単にHighに維持されている場合はリセットシーケンスを開始しません。

- local_reset_reqへの追加パルスは、リセットシーケンスが完了するまで無視されます。

オプション: local_reset_doneのデアサートとアサートの検出

必要な場合は、local_reset_done信号の状態を監視し、リセットシーケンスの状態を明示的に検出することができます。

- EMIF IPは、リセット要求を受信すると、local_reset_done信号をデアサートします。電源投入時の初期のキャリブレーション後、local_reset_doneはユーザーが要求するリセットに応じてのみデアサートされます。実際のタイミングは現在のI/O SSMの状態に依存しますが、local_reset_doneがLowに遷移すると、リセットシーケンスは間近に迫っています。EMIFリセットシーケンスの一部として、コアのリセット信号 (emif_usr_reset_n、afi_reset_n) がLowに駆動されます。コアのリセット信号によるレジスターリセットでlocal_reset_doneをサンプリングしないでください。

- リセットシーケンスが完了すると、local_reset_doneは再度Highに駆動されます。Highに駆動されているlocal_reset_doneは、リセットシーケンスの完了、および新しいリセット要求の受け入れ準備ができていることを示します。ただし、キャリブレーションが成功したことや、ハード・メモリー・コントローラーで要求を受け入れる準備ができていることを意味するものではありません。これらの点に関しては、ユーザーロジックでafi_cal_success、afi_cal_fail、local_cal_success、local_cal_fail、amm_readyなどの信号を確認する必要があります。