インテルのみ表示可能 — GUID: ail1652141703276

Ixiasoft

1. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPについて

2. インテル® Agilex™ FPGA EMIF IP – 概要

3. インテル® Agilex™ FPGA EMIF IP - 製品アーキテクチャー

4. インテル® Agilex™ FPGA EMIF IP - エンドユーザーの信号

5. インテル® Agilex™ FPGA EMIF IP - メモリーIPのシミュレーション

6. インテル® Agilex™ FPGA EMIF IP – DDR4のサポート

7. インテル® Agilex™ FPGA EMIF IP - QDR-IVのサポート

8. インテル® Agilex™ FPGA EMIF IP – タイミング・クロージャー

9. インテル® Agilex™ FPGA EMIF IP – I/Oのタイミング・クロージャー

10. インテル® Agilex™ FPGA EMIF IP – コントローラーの最適化

11. インテル® Agilex™ FPGA EMIF IP – デバッグ

12. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPユーザーガイド・アーカイブ

13. 外部メモリー・インターフェイス・ インテル® Agilex™ FPGA IPユーザーガイドの改訂履歴

3.1.1. インテル® Agilex™ EMIFのアーキテクチャー: I/Oサブシステム

3.1.2. インテル® Agilex™ EMIFのアーキテクチャー: I/O SSM

3.1.3. インテル® Agilex™ EMIFのアーキテクチャー: I/Oバンク

3.1.4. インテル® Agilex™ EMIFのアーキテクチャー: I/Oレーン

3.1.5. インテル® Agilex™ EMIFのアーキテクチャー: 入力DQSクロックツリー

3.1.6. インテル® Agilex™ EMIFのアーキテクチャー: PHYクロックツリー

3.1.7. インテル® Agilex™ EMIFのアーキテクチャー: PLLリファレンス・クロック・ネットワーク

3.1.8. インテル® Agilex™ EMIFのアーキテクチャー: クロックの位相アライメント

3.3.4.3.1. キャリブレーション・レポートの情報を使用してのキャリブレーション・エラーのデバッグ

3.3.4.3.2. アドレスおよびコマンドのレベリング・キャリブレーション・エラーのデバッグ

3.3.4.3.3. アドレスおよびコマンドのデスキューエラーのデバッグ

3.3.4.3.4. DQSイネーブルエラーのデバッグ

3.3.4.3.5. 読み出しのデスキュー・キャリブレーション・エラーのデバッグ

3.3.4.3.6. VREFINキャリブレーション・エラーのデバッグ

3.3.4.3.7. LFIFOキャリブレーション・エラーのデバッグ

3.3.4.3.8. 書き込みレベリングエラーのデバッグ

3.3.4.3.9. 書き込みのデスキュー・キャリブレーション・エラーのデバッグ

3.3.4.3.10. VREFOUTキャリブレーション・エラーのデバッグ

4.1.1.1. DDR4のlocal_reset_req

4.1.1.2. DDR4のlocal_reset_status

4.1.1.3. DDR4のpll_ref_clk

4.1.1.4. DDR4のpll_locked

4.1.1.5. DDR4のac_parity_err

4.1.1.6. DDR4のoct

4.1.1.7. DDR4のmem

4.1.1.8. DDR4のstatus

4.1.1.9. DDR4のafi_reset_n

4.1.1.10. DDR4のafi_clk

4.1.1.11. DDR4のafi_half_clk

4.1.1.12. DDR4のafi

4.1.1.13. DDR4のemif_usr_reset_n

4.1.1.14. DDR4のemif_usr_clk

4.1.1.15. DDR4のctrl_amm

4.1.1.16. DDR4のctrl_amm_aux

4.1.1.17. DDR4のctrl_auto_precharge

4.1.1.18. DDR4のctrl_user_priority

4.1.1.19. DDR4のctrl_ecc_user_interrupt

4.1.1.20. DDR4のctrl_ecc_readdataerror

4.1.1.21. DDR4のctrl_ecc_status

4.1.1.22. DDR4のctrl_mmr_slave

4.1.1.23. DDR4のhps_emif

4.1.1.24. DDR4のemif_calbus

4.1.1.25. DDR4のemif_calbus_clk

4.1.2.1. QDR-IVのlocal_reset_req

4.1.2.2. QDR-IVのlocal_reset_status

4.1.2.3. QDR-IVのpll_ref_clk

4.1.2.4. QDR-IVのpll_locked

4.1.2.5. QDR-IVのoct

4.1.2.6. QDR-IVのmem

4.1.2.7. QDR-IVのstatus

4.1.2.8. QDR-IVのafi_reset_n

4.1.2.9. QDR-IVのafi_clk

4.1.2.10. QDR-IVのafi_half_clk

4.1.2.11. QDR-IVのafi

4.1.2.12. QDR-IVのemif_usr_reset_n

4.1.2.13. QDR-IVのemif_usr_clk

4.1.2.14. QDR-IVのctrl_amm

4.1.2.15. QDR-IVのemif_calbus

4.1.2.16. QDR-IVのemif_calbus_clk

4.4.1. ctrlcfg0

4.4.2. ctrlcfg1

4.4.3. dramtiming0

4.4.4. sbcfg1

4.4.5. caltiming0

4.4.6. caltiming1

4.4.7. caltiming2

4.4.8. caltiming3

4.4.9. caltiming4

4.4.10. caltiming9

4.4.11. dramaddrw

4.4.12. sideband0

4.4.13. sideband1

4.4.14. sideband4

4.4.15. sideband6

4.4.16. sideband7

4.4.17. sideband9

4.4.18. sideband11

4.4.19. sideband12

4.4.20. sideband13

4.4.21. sideband14

4.4.22. dramsts

4.4.23. niosreserve0

4.4.24. niosreserve1

4.4.25. sideband16

4.4.26. ecc3: ECCエラーおよび割り込みのコンフィグレーション

4.4.27. ecc4: ステータスとエラー情報

4.4.28. ecc5: 最新のSBEまたはDBEのアドレス

4.4.29. ecc6: 最新のドロップされた訂正コマンドのアドレス

4.4.30. ecc7: 最新のSBEまたはDBEのアドレスの拡張

4.4.31. ecc8: 最新のドロップされた訂正コマンドのアドレスの拡張

6.1.1. インテルAgilex EMIF IPにおけるDDR4のパラメーター: General

6.1.2. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Memory

6.1.3. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Mem I/O

6.1.4. インテルAgilex EMIF IPにおけるDDR4のパラメーター: FPGA I/O

6.1.5. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Mem Timing

6.1.6. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Controller

6.1.7. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Diagnostics

6.1.8. インテルAgilex EMIF IPにおけるDDR4のパラメーター: Example Designs

7.1.1. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: General

7.1.2. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Memory

7.1.3. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: FPGA I/O

7.1.4. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Mem Timing

7.1.5. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Controller

7.1.6. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Diagnostics

7.1.7. インテルAgilex EMIF IPにおけるQDR-IVのパラメーター: Example Designs

11.1. インターフェイスのコンフィグレーションにおける性能の問題

11.2. 機能的な問題の評価

11.3. タイミング問題の特徴

11.4. Signal Tapロジック・アナライザーでのメモリーIPの検証

11.5. ハードウェアのデバッグ・ガイドライン

11.6. ハードウェアの問題の分類

11.7. 外部メモリー・インターフェイス・デバッグ・ツールキットを使用したデバッグ

11.8. デフォルトのトラフィック・ジェネレーターの使用

11.9. コンフィグレーション可能なトラフィック・ジェネレーター (TG2) の使用

11.10. EMIFオンチップ・デバッグ・ポート

11.11. Efficiency Monitor

11.7.4.3.1. キャリブレーション・レポートの情報を使用してのキャリブレーション・エラーのデバッグ

11.7.4.3.2. アドレスおよびコマンドのレベリング・キャリブレーション・エラーのデバッグ

11.7.4.3.3. アドレスおよびコマンドのデスキューエラーのデバッグ

11.7.4.3.4. DQSイネーブルエラーのデバッグ

11.7.4.3.5. 読み出しのデスキュー・キャリブレーション・エラーのデバッグ

11.7.4.3.6. VREFINキャリブレーション・エラーのデバッグ

11.7.4.3.7. LFIFOキャリブレーション・エラーのデバッグ

11.7.4.3.8. 書き込みレベリングエラーのデバッグ

11.7.4.3.9. 書き込みのデスキュー・キャリブレーション・エラーのデバッグ

11.7.4.3.10. VREFOUTキャリブレーション・エラーのデバッグ

インテルのみ表示可能 — GUID: ail1652141703276

Ixiasoft

5.3.4. ed_sim.vファイルの編集

- テキストエディターで、ed_sim.vファイルを開きます。このファイルは、<example design_path>/sim/ed_sim/simフォルダーにあります。

- 次のラインをed_sim.vファイルに追加し、マスター・テスト・プログラム・インスタスを含めます。

//Edit 1 : To connect local_cal_sucess to ARESETn of AXI4 Master BFM wire local_cal_success; //Edit 2 : To include master test program instance master_test_program #( .AXI4_ADDRESS_WIDTH (33), .AXI4_RDATA_WIDTH (32), .AXI4_WDATA_WIDTH (32), .AXI4_ID_WIDTH (18), .AXI4_USER_WIDTH (8), .AXI4_REGION_MAP_SIZE (16)) u_master (mgc_axi4_master_0.mgc_axi4_master_0);

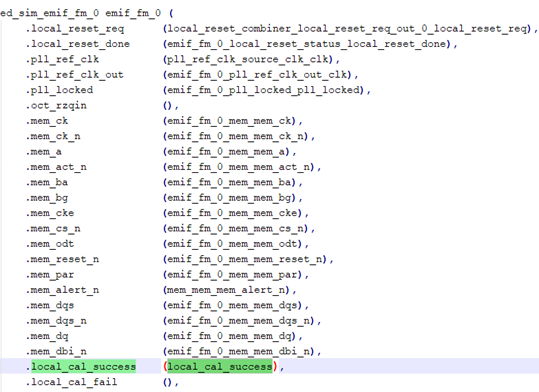

- emif_fm_0のlocal_cal_successをAXI4 Master BFMのARESETnに接続します。これを行うことにより、EMIFキャリブレーションが成功するまで、BFMがトランザクションを発行しないようにします。

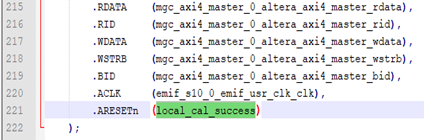

図 107. EMIF IP接続での編集

図 108. AXI4 Master BFM接続での編集

図 108. AXI4 Master BFM接続での編集