インテルのみ表示可能 — GUID: mwh1410383715310

Ixiasoft

インテルのみ表示可能 — GUID: mwh1410383715310

Ixiasoft

2.6.5.3. 生成されるクロックの作成 (create_generated_clock)

生成クロックは一般的に、PLL の出力、レジスタークロックの分周器、クロック・マルチプレクサー、および、FPGA 出力ポートから他のデバイスに転送されるクロック (ソース・シンクロナス・インターフェイスやメモリー・インターフェイスなど) に適用されます。.sdc ファイルでは、ベースクロックの定義後に生成クロックを入力します。生成クロックでは、生成クロックのターゲットに対するクロック遅延とクロック・レイテンシーがすべて自動的に考慮されます。

-source オプションではクロックパス内のノード名を指定し、生成されるクロックのリファレンスとして使用します。生成されるクロックのソースは、先ほど定義したクロック名ではなく、デザイン・ネットリストのノードにする必要があります。生成クロックのターゲットの入力クロックピンと、そのリファレンス・クロックのターゲットノードの間のクロックパスにある任意のノード名をソースノードとして使用することができます。

ターゲットノードの入力クロックピンを新しく生成されるクロックのソースとして指定します。生成クロックのソースクロックとしてノードを受け入れることで、生成クロックの制約がクロックソースから切り離されます。生成クロックのソースクロックを変更する際に、ソースノードが同じ場合は、生成クロックの制約を編集する必要はありません。

複数のベースクロックがノードに供給されており、そのノードを生成クロックのソースにする場合は、複数の生成クロックを定義する必要があります。生成される各クロックに 1 つのベースクロックを関連付けます。それには、各生成クロックのステートメントで -master_clock オプションを使用します。場合によっては、生成クロックは組み合わせロジックで生成されます。

クロックを変更するロジックの合成方法に応じて、ソースまたはターゲットのノードはコンパイルごとに変わることがあります。生成クロックの制約を書き込み後に名前が変わると、コンパイラーで生成クロックが無視されます。これは、そのターゲット名がデザインに存在しなくなるために起こります。この問題を回避するには、合成属性または合成割り当てを使用して、クロック変更ロジックの最終的な組み合わせノード名を維持します。次に、その維持された名前を生成クロックの制約で使用します。

ノードで生成クロックを作成し、そのクロックで最終的にレジスターのデータ入力を供給する場合は、「データとしてのクロック」という特殊なケースになります。タイミング・アナライザーはデータとしてのクロックを異なる方法で処理します。例えば、DDR でデータとしてのクロックを使用する場合、このクロックの立ち上がりと立ち下がりの両方を考慮する必要があり、タイミング・アナライザーでは立ち上がりと立ち下がりの両方が報告されます。データとしてのクロックを使用すると、コンパイラーは、From Node を生成クロックのターゲットとして扱い、Launch Clock を生成クロックとして扱います。

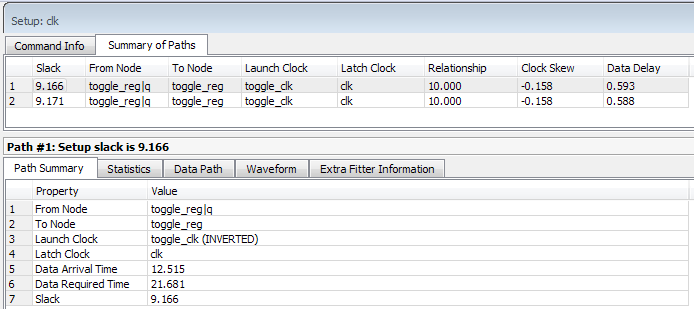

データとしてのクロックの例の場合、最初のパスは toggle_clk (INVERTED) から clk で、2 番目のパスは toggle_clk から clk です。これらのケースのスラックは、パスに沿った立ち上がり時間と立ち下がり時間の違いによりわずかに異なります。Data Delay 列には、約 5ps の差が報告されています。最小のスラック値をもつパスのみを考慮する必要があります。タイミング・アナライザーは、2 つのうちのワーストケース・パスのみを報告します (立ち上がりと立ち下がり)。この例で、生成クロックをレジスター出力で定義しない場合は、タイミング解析は最小スラック値をもつパスを 1 つだけ報告します。

derive_pll_clocks コマンドを使用して、すべての PLL クロック出力にクロックを自動的に生成することができます。PLL 出力における生成クロックのプロパティーは、PLL に定義されているプロパティーと一致します。