インテルのみ表示可能 — GUID: ptu1614354759820

Ixiasoft

2.1. タイミング解析フロー

2.2. ステップ 1: タイミング・アナライザーの設定を指定

2.3. ステップ 2: タイミング制約の指定

2.4. ステップ 3: タイミング・アナライザーの実行

2.5. ステップ 4: タイミングレポートの解析

2.6. タイミング制約の適用

2.7. タイミング・アナライザーの Tcl コマンド

2.8. インポートされたコンパイル結果のタイミング解析

2.9. インテル® Quartus® Prime タイミング・アナライザー・ユーザーガイドの改訂履歴

2.10. インテル® Quartus® Primeプロ・エディションのユーザーガイド: タイミング・アナライザーのアーカイブ

2.5.1.1. Fmax 概要レポート

2.5.1.2. タイミングレポート

2.5.1.3. ソースファイルごとのタイミングレポート

2.5.1.4. データ遅延レポート

2.5.1.5. ネット遅延レポート

2.5.1.6. クロックレポートおよびクロック・ネットワーク・レポート

2.5.1.7. クロック間転送レポート

2.5.1.8. メタスタビリティー・レポート

2.5.1.9. CDC Viewer レポート

2.5.1.10. 非同期 CDC レポート

2.5.1.11. ロジック深度レポート

2.5.1.12. 近隣パスレポート

2.5.1.13. レジスター分布レポート

2.5.1.14. ルーティング着目ネットレポート

2.5.1.15. リタイミング制約レポート

2.5.1.16. レジスター統計情報レポート

2.5.1.17. パイプライン情報レポート

2.5.1.18. 時間借用データレポート

2.5.1.19. 例外レポートおよび例外範囲レポート

2.5.1.20. ボトルネック・レポート

2.6.8.5.1. デフォルトのマルチサイクル解析

2.6.8.5.2. エンド・マルチサイクル・セットアップ = 2、エンド・マルチサイクル・ホールド = 0

2.6.8.5.3. エンド・マルチサイクル・セットアップ = 2、エンド・マルチサイクル・ホールド = 1

2.6.8.5.4. 同じ周波数のクロック (送信先クロックのオフセットあり)

2.6.8.5.5. 送信元クロック周波数の倍数になる送信先クロック周波数

2.6.8.5.6. 送信元クロック周波数の倍数になる送信先クロック周波数 (オフセットあり)

2.6.8.5.7. 送信先クロック周波数の倍数になる送信元クロック周波数

2.6.8.5.8. 送信先クロック周波数の倍数になる送信元クロック周波数 (オフセットあり)

インテルのみ表示可能 — GUID: ptu1614354759820

Ixiasoft

2.5.1.16. レジスター統計情報レポート

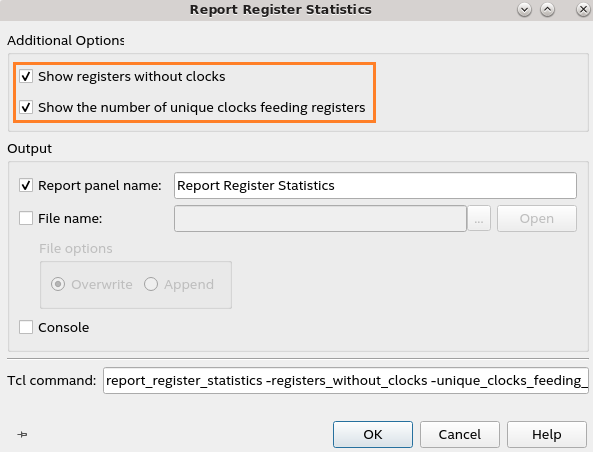

タイミング・アナライザーの Reports > Design Metrics > Report Register Statistics コマンドでは、デザイン内の同期および非同期リセット、ハイパーレジスター、クロックイネーブルを備えるレジスターの数を示すことができます。 この情報をタイミングスラック、輻輳、および他の解析レポートと組み合わせて使用することで、デザインのタイミングがクリティカルな部分でリセットを除外したり、制御スキームを変更したりできるかを判断し、タイミング要件をより効率的に満たすことができます。

図 71. Report Register Statistics

注:

- このレポートは、合成後 (DNI Flow) とプランニング後のタイミング解析の両方で同様に機能します。ただし、レポートの Without a Clock 列は、合成後のタイミング解析でより効果的に使用することができます。従来の SDC (RTL での SDC 以外) は通常、合成後のモードでロードされないため、このレポートを使用して、SDC がない場合にタイミングが受ける影響を解析することができます。

- derive_clocks コマンドで生成されたクロックは、ユーザークロックとしてカウントされません。

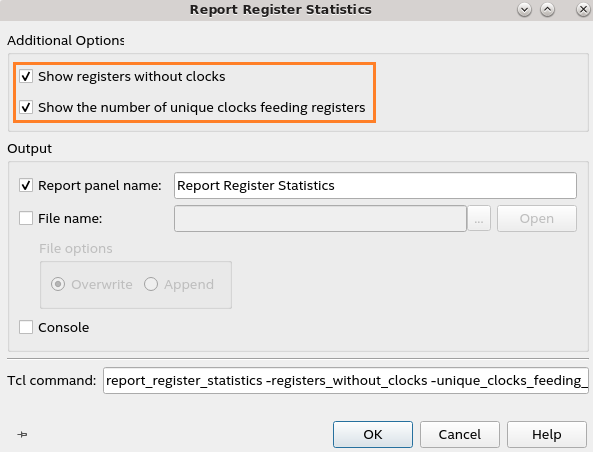

Without a Clock 列は、Register Count 列に示されている階層のレジスターにおいて、定義されたクロックが供給されていないレジスターの数を示します。この列の値が 0 の場合は、デザインに SDC 定義のクロックがあり、デザイン内のレジスターに供給されていることを示しています。Unique Clocks 列は、Register Count で特定されている階層内のレジスターに供給される一意の SDC 定義クロックの数を示しています。これらの列を表示するには、レポートを実行する際に表示されるダイアログで、Show registers without clocks および Show the number of unique clocks feeding registers 追加オプションを有効にします。次の図に詳細を示します。

図 72. Report Register Statistics ダイアログの追加オプション