インテルのみ表示可能 — GUID: mwh1410383855277

Ixiasoft

2.1. タイミング解析フロー

2.2. ステップ 1: タイミング・アナライザーの設定を指定

2.3. ステップ 2: タイミング制約の指定

2.4. ステップ 3: タイミング・アナライザーの実行

2.5. ステップ 4: タイミングレポートの解析

2.6. タイミング制約の適用

2.7. タイミング・アナライザーの Tcl コマンド

2.8. インポートされたコンパイル結果のタイミング解析

2.9. インテル® Quartus® Prime タイミング・アナライザー・ユーザーガイドの改訂履歴

2.10. インテル® Quartus® Primeプロ・エディションのユーザーガイド: タイミング・アナライザーのアーカイブ

2.5.1.1. Fmax 概要レポート

2.5.1.2. タイミングレポート

2.5.1.3. ソースファイルごとのタイミングレポート

2.5.1.4. データ遅延レポート

2.5.1.5. ネット遅延レポート

2.5.1.6. クロックレポートおよびクロック・ネットワーク・レポート

2.5.1.7. クロック間転送レポート

2.5.1.8. メタスタビリティー・レポート

2.5.1.9. CDC Viewer レポート

2.5.1.10. 非同期 CDC レポート

2.5.1.11. ロジック深度レポート

2.5.1.12. 近隣パスレポート

2.5.1.13. レジスター分布レポート

2.5.1.14. ルーティング着目ネットレポート

2.5.1.15. リタイミング制約レポート

2.5.1.16. レジスター統計情報レポート

2.5.1.17. パイプライン情報レポート

2.5.1.18. 時間借用データレポート

2.5.1.19. 例外レポートおよび例外範囲レポート

2.5.1.20. ボトルネック・レポート

2.6.8.5.1. デフォルトのマルチサイクル解析

2.6.8.5.2. エンド・マルチサイクル・セットアップ = 2、エンド・マルチサイクル・ホールド = 0

マルチサイクル制約

2.6.8.5.3. エンド・マルチサイクル・セットアップ = 2、エンド・マルチサイクル・ホールド = 1

2.6.8.5.4. 同じ周波数のクロック (送信先クロックのオフセットあり)

2.6.8.5.5. 送信元クロック周波数の倍数になる送信先クロック周波数

2.6.8.5.6. 送信元クロック周波数の倍数になる送信先クロック周波数 (オフセットあり)

2.6.8.5.7. 送信先クロック周波数の倍数になる送信元クロック周波数

2.6.8.5.8. 送信先クロック周波数の倍数になる送信元クロック周波数 (オフセットあり)

インテルのみ表示可能 — GUID: mwh1410383855277

Ixiasoft

2.6.8.5.2. エンド・マルチサイクル・セットアップ = 2、エンド・マルチサイクル・ホールド = 0

この例で、エンド・マルチサイクル・セットアップの割り当て値は 2、エンド・マルチサイクル・ホールドの割り当て値は 0 です。

マルチサイクル制約

set_multicycle_path -from [get_clocks clk_src] -to [get_clocks clk_dst] \

-setup -end 2

注: デフォルトのエンド・マルチサイクル・ホールド値は 0 であるため、タイミング・アナライザーは、エンド・マルチサイクル・ホールド値を必要としません。

この例では、セットアップ関係を 1 クロック周期緩和するために、ラッチエッジを次のラッチエッジに動かしています。ホールド解析はデフォルトの設定から変化しません。次に、タイミング・アナライザーが実行する解析のセットアップ・タイミング図を示します。ラッチエッジは、デフォルトのシングルサイクル解析よりも 1 クロックサイクル遅くなります。

図 118. セットアップのタイミング図この図は、タイミング・アナライザーが実行する解析のセットアップ・タイミング図を示しています。マルチサイクル制約がない場合、ラッチエッジはエッジ 1 です。ただし、マルチサイクル制約がある場合、ラッチエッジはエッジ 2 になります。

図 119. セットアップ・チェックの計算

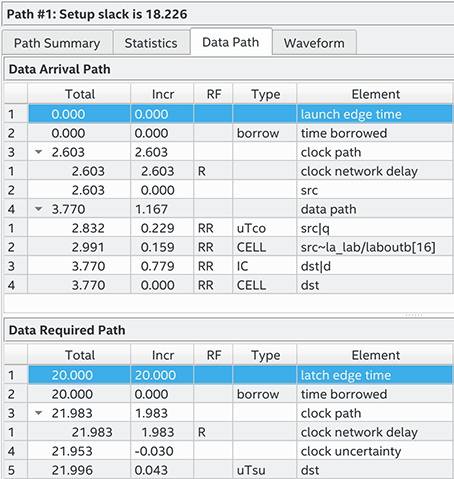

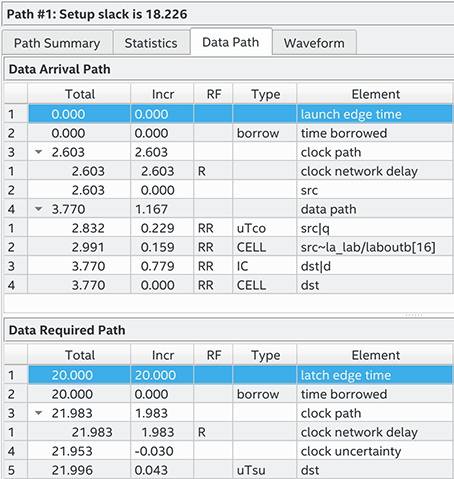

最も制約が厳しいセットアップ関係は、エンド・マルチサイクル・セットアップ割り当てが 2 の場合の 20ns です。次の図は、タイミング・アナライザーのセットアップ・レポートで、起動エッジとラッチエッジが強調表示されています。

図 120. セットアップ・マルチサイクル例外のあるセットアップ・レポート

マルチサイクル・ホールドのラッチエッジおよび起動エッジは、デフォルト設定でのホールド解析の結果と同じになるため、この例のマルチサイクル・ホールド解析は、シングルサイクルのホールド解析と同等になります。ホールドチェックは、セットアップ・チェックに相対します。通常、タイミング・アナライザーは、最も制約が厳しいセットアップ・チェックのエッジだけでなく、考えられるすべてのセットアップ・チェックでホールドチェックを実行します。

図 121. ホールドのタイミング図この図は、ホールドのラッチエッジが 0ns と 10ns ではなく、10ns と 20ns であることを示しています。

図 122. セットアップ・マルチサイクル例外のあるホールドレポート

図 123. ホールドチェックの計算