インテルのみ表示可能 — GUID: xbg1615854170190

Ixiasoft

1. F タイルの概要

2. F タイルのアーキテクチャー

3. F-Tile PMA/FEC Direct PHY Intel® FPGA IP の実装

4. F-Tile Reference and System PLL Clocks Intel® FPGA IP の実装

5. F タイル PMA/FEC Direct PHY デザインの実装

6. サポートされるツール

7. F タイル・トランシーバー・リンクのデバッグ

8. F タイルのアーキテクチャーと PMA および FEC Direct PHY IP のユーザーガイド・アーカイブ

9. F タイルのアーキテクチャーと PMA および FEC Direct PHY IP のユーザーガイド改訂履歴

A. 付録

2.2.2.1. 400G ハード IP と FHT を使用している 1 つの 200GbE-4 インターフェイスの実装

2.2.2.2. 400G ハード IP と FHT を使用している 1 つの 200GbE-2 インターフェイスの実装

2.2.2.3. 400G ハード IP と FHT を使用している 1 つの 100GbE-1 インターフェイスの実装

2.2.2.4. 400G ハード IP と FGT を使用している 1 つの 100GbE-4 インターフェイスの実装

2.2.2.5. 200G ハード IP と FGT を使用している 1 つの 10GbE-1 インターフェイスの実装

2.2.2.6. 400G ハード IP と FHT を使用している 3 つの 25GbE-1 インターフェイスの実装

2.2.2.7. 400G ハード IP と FHT を使用している 1 つの 50GbE-1 インターフェイスと 2 つの 25GbE-1 インターフェイスの実装

2.2.2.8. 400G ハード IP と FHT を使用している 1 つの 100GbE-1 インターフェイスと 2 つの 25GbE-1 インターフェイスの実装

2.2.2.9. 400G ハード IP と FHT を使用している 2 つの 100GbE-1 インターフェイスと 1 つの 25GbE-1 インターフェイスの実装

2.2.2.10. 400G ハード IP と FHT を使用している 100GbE-1、100GbE-2、および 50GbE-1 インターフェイスの実装

3.1. F-Tile PMA/FEC Direct PHY Intel® FPGA IP の概要

3.2. F-Tile PMA/FEC Direct PHY Intel® FPGA IP を使用するデザイン

3.3. IP のコンフィグレーション

3.4. 信号とポートのリファレンス

3.5. PMA および FEC モードにおける PHY TX および RX データパスのビットマッピング

3.6. クロック

3.7. カスタム拍生成ポートとロジック

3.8. リセットのアサート

3.9. ボンディングの実装

3.10. 独立したポートのコンフィグレーション

3.11. コンフィグレーション・レジスター

3.12. コンフィグレーション可能な インテル® Quartus® Prime 開発ソフトウェアの設定

3.13. ハードウェア・テストに向けた F-Tile PMA/FEC Direct PHY Intel® FPGA IP のコンフィグレーション

3.14. Avalon® メモリーマップド・インターフェイスを使用してのハードウェア・コンフィグレーション

3.4.1. TX および RX のパラレルおよびシリアル・インターフェイス信号

3.4.2. TX および RX のリファレンス・クロックとクロック出力インターフェイス信号

3.4.3. リセット信号

3.4.4. RS-FEC の信号

3.4.5. カスタム拍のコントロールおよびステータス信号

3.4.6. TX PMA のコントロール信号

3.4.7. RX PMA のステータス信号

3.4.8. TX/RX の PMA およびコア・インターフェイス FIFO の信号

3.4.9. PMA Avalon® メモリーマップド・インターフェイスの信号

3.4.10. データパス Avalon® メモリーマップド・インターフェイスの信号

5.1. F タイル PMA/FEC Direct PHY デザインの実装

5.2. F-Tile PMA/FEC Direct PHY Intel® FPGA IP のインスタンス化

5.3. F-Tile PMA/FEC Direct PHY Intel® FPGA IP での RS-FEC Direct デザインの実装

5.4. F-Tile Reference and System PLL Clocks Intel® FPGA IP のインスタンス化

5.5. カスタム拍生成ポートとロジックのイネーブル

5.6. F タイル PMA/FEC Direct PHY デザインの IP の接続

5.7. F タイル PMA/FEC Direct PHY デザインのシミュレーション

5.8. F タイル・インターフェイスのプランニング

インテルのみ表示可能 — GUID: xbg1615854170190

Ixiasoft

5.4. F-Tile Reference and System PLL Clocks Intel® FPGA IP のインスタンス化

F タイル PMA/FEC Direct PHY のデザインでは、F-Tile Reference and System PLL Clocks Intel® FPGA IP が必要です。シミュレーションとコンパイルには、この IP をインスタンス化して接続する必要があります。

このデザインでは、F-Tile Reference and System PLL Clocks Intel® FPGA IP に以下が必要です。

- 1 つのシステム PLL に対するシステム PLL のモードとリファレンス・クロック・ソース。これは、データパスのクロックになります。

- FGT PMA のリファレンス・クロック・ソース。システム PLL と FGT PMA のリファレンス・クロック・ソースは、共有または個別にします。この例では、リファレンス・クロックを共有します。

1 つのシステム PLL に対するシステム PLL のモードとリファレンス・クロック・ソースを指定するには、次の手順に従います。

- IP Catalog の検索フィールドに f-tile Reference と入力し、Transceiver PHY にある F-Tile Reference and System PLL Clocks Intel® FPGA IP をダブルクリックします。

- System PLL #0 タブで、次のパラメーターを指定します。

表 99. System PLL #0 のオプション パラメーター パラメーター値 Mode of system PLL ETHERNET_FREQ_830_156 を選択します。これは、システム PLL の入力周波数を 156.25Mhz、出力周波数を 830.078125MHz にコンフィグレーションします (F-Tile PMA/FEC Direct PHY Intel® FPGA IP のシステム PLL 周波数に一致する必要があります)。 Refclk source RefClk #0。システム PLL のリファレンス・クロック・ソースを選択します。 RefClk #0 for FGT PMA オンにします。 - RefClk で、次のオプションを指定します。

表 100. RefClk のオプション パラメーター パラメーター値 Enable RefClk #0 for FGT PMA オンにします。このリファレンス・クロックは、システム PLL #0 と FGT PMA で共有されます。 RefClk source RefClk #0。156.25MHz (F-Tile PMA/FEC Direct PHY Intel® FPGA IP のリファレンス・クロック周波数と同じ)。

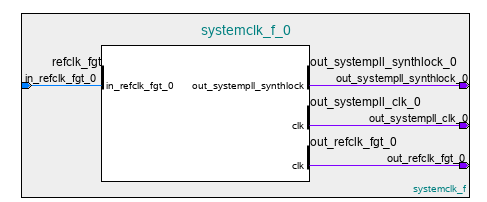

図 103. システム PLL と RefClk のオプション

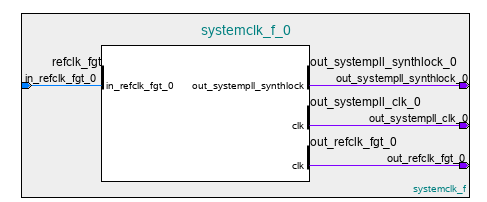

次の図は、この例における F-Tile Reference and System PLL Clocks Intel® FPGA IP のブロック記号と利用可能なポートを表しています。

図 104. F-Tile Reference and System PLL Clocks Intel® FPGA IP 例のポート