インテルのみ表示可能 — GUID: ksw1487372637420

Ixiasoft

7.1.1. レジスターアクセスの定義

7.1.2. PCIコンフィグレーション・ヘッダー・レジスター

7.1.3. PCI Express機能構造

7.1.4. インテル定義のVSEC Capabilityヘッダー

7.1.5. Uncorrectable Internal Error Status (修正不可能な内部エラーステータス) レジスター

7.1.6. Uncorrectable Internal Error Mask (修正不可能な内部エラーマスク) レジスター

7.1.7. Correctable Internal Error Status (修正可能な内部エラーステータス) レジスター

7.1.8. Correctable Internal Error Mask (修正可能な内部エラーマスク) レジスター

10.5.1. ebfm_barwrプロシージャー

10.5.2. ebfm_barwr_immプロシージャー

10.5.3. ebfm_barrd_waitプロシージャー

10.5.4. ebfm_barrd_nowtプロシージャー

10.5.5. ebfm_cfgwr_imm_waitプロシージャー

10.5.6. ebfm_cfgwr_imm_nowtプロシージャー

10.5.7. ebfm_cfgrd_waitプロシージャー

10.5.8. ebfm_cfgrd_nowtプロシージャー

10.5.9. BFMコンフィグレーション・プロシージャー

10.5.10. BFM共有メモリー・アクセス・プロシージャー

10.5.11. BFMログおよびメッセージ・プロシージャー

10.5.12. Verilog HDL Formattingファンクション

インテルのみ表示可能 — GUID: ksw1487372637420

Ixiasoft

8.2. 書き込みDMAの例

この例では、3つのデータブロックをAvalon-MM空間からPCIeアドレス空間 (システムメモリー) に移動させます。

注: 17.1リリース以降、インテルQuartus Primeプロ・エディション開発ソフトウェアは、パラメーター・エディターを使用して指定したパラメーターのデザイン例を動的に生成します。したがって、インテルQuartus Primeプロ・エディションのインストール・ディレクトリーは、インテルStratix 10デバイスのスタティック・デザイン例を提供しなくなりました。スタティック・デザイン例は、 インテル® Arria® 10および インテル® Cyclone® 10デバイスを含む、以前のデバイスファミリーで使用可能です。

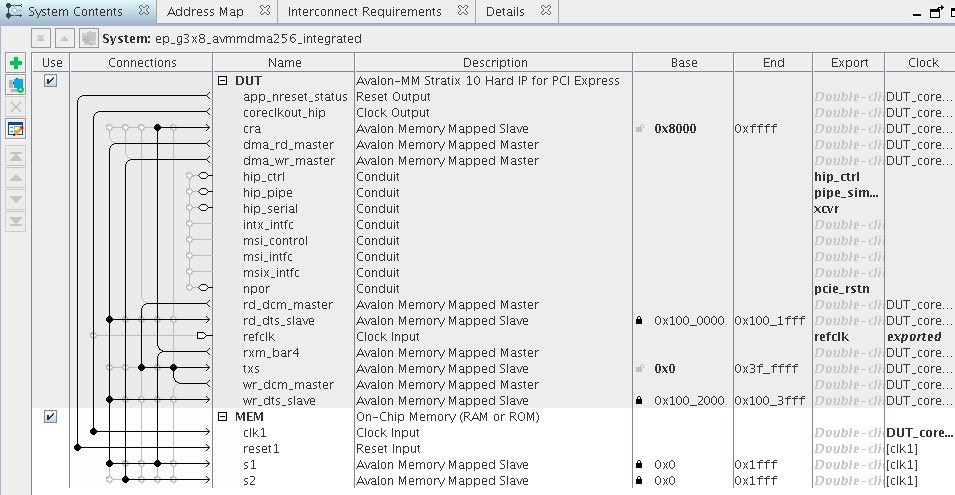

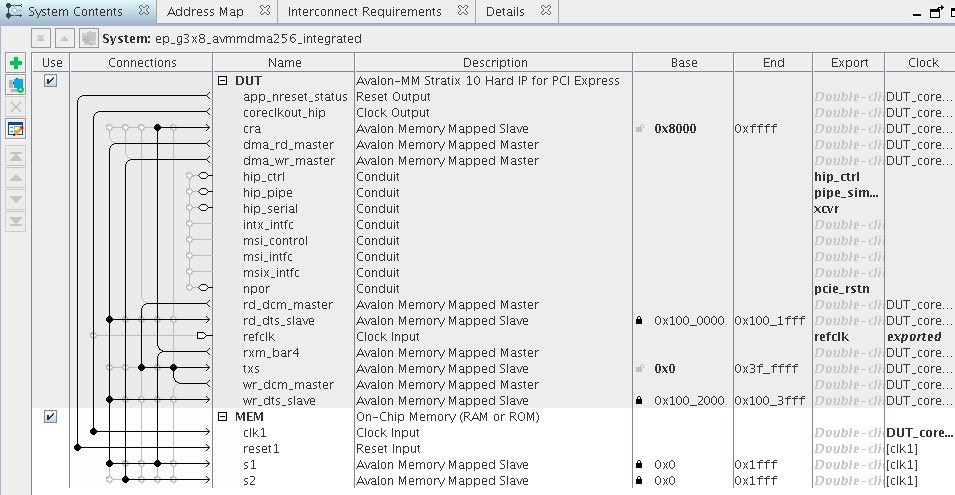

図 63. インテルStratix 10 Gen3 x8 Avalon-MM DMA統合のプラットフォーム・デザイナー

次の図は、PCIeおよび-MMアドレス空間のデータブロックの位置とサイズ、およびディスクリプター・テーブルのフォーマットを示しています。この例では、RD_TABLE_SIZE の値は127です。

図 64. 書き込みDMAを使用してAvalon-MMアドレス空間からPCIeシステムメモリーに転送するデータブロック

ディスクリプター・テーブルには、128のエントリーが含まれています。ステータステーブルは、メモリー内の可変数のディスクリプターの前にあります。ReadおよびWrite StatusとDescriptor Tableは、それぞれ Read Descriptor Base Register および Write Descriptor Base Register で指定されたアドレスにあります。

図 65. PCIe* システムメモリー内のディスクリプター・テーブル

- ソフトウェアは、ホストメモリー内のWrite Descriptor StatusテーブルおよびWrite Descriptor Controllerテーブルのメモリーを割り当てます。メモリー割り当てには、次の計算が必要です。

- 書き込みステータステーブルの各エントリーは4バイトです。128の書き込みエントリーには、512バイトのメモリーが必要です。

- 各ディスクリプターは32バイトです。3つのディスクリプターには、96バイトのメモリーが必要です。

注: 起こり得るオーバーフロー状態を回避するには、ディスクリプターの初期数ではなく、RD_TABLE_SIZE によってサポートされるディスクリプターの数に必要なメモリーを割り当てます。

ソフトウェアがステータステーブルおよびディスクリプター・テーブルに割り当てる必要のあるメモリーの合計は、608バイトです。Write Descriptor Controller Statusテーブルは、Read Descriptor Controller Statusテーブルに続きます。Read Statusテーブルのエントリーには、512バイトのメモリーが必要です。したがって、Write Descriptor Statusテーブルは0xF000_0200から始まります。 - 図 64 に示すアドレスからのオフセット0x200から始まるWrite Descriptor Controllerテーブルをプログラムします。3つのデータブロックには、3つのディスクリプターが必要です。

- ディスクリプター・テーブルの開始アドレスを使用して、Write Descriptor Controllerの Write Status and Descriptor Base レジスターをプログラムします。

- オンチップ書き込みディスクリプター・テーブルFIFOの開始アドレスで、Write Descriptor Controllerの Write Descriptor FIFO Base を、プログラムします。これは、プラットフォーム・デザイナーの wr_dts_slave ポートのベースアドレスです。この例では、アドレスは0x0100_0200です。

図 66. オンチップ書き込みFIFOのアドレス

- 各ディスクリプターのステータス更新を取得するには、Write Descriptor Controllerレジスター WR_CONTROL を0x1でプログラムします。この手順はオプションです。

- Write Descriptor Controllerレジスター WR_DMA_LAST_PTR に値3をプログラムします。このレジスターに書き込むと、Write Descriptor Controllerディスクリプター・テーブルのフェッチプロセスがトリガーされます。したがって、このレジスターへの書き込みは、DMA転送をセットアップする最後の手順である必要があります。

- ホストはMSI割り込みを待ちます。Write Descriptor Controllerは、最後のディスクリプターの完了後、MSIをホストに送信します。Write Descriptor Controllerは、Update も書き込みます。

- 移動させる追加のデータブロックがある場合は、次の手順を実行して、追加の転送を設定します。

- メモリーアドレス0xF000_0200 + (<前の最後のディスクリプター・ポインター> * 0x20) から始まるディスクリプター・テーブルをプログラムします。この場合、ディスクリプター・ポインターは3でした。

- Write Descriptor Controllerレジスター WR_DMA_LAST_PTR を、previous_value (3 in this case) + number of new descriptors でプログラムします。このレジスターに書き込むと、Write Descriptor Controllerディスクリプター・テーブルのフェッチプロセスがトリガーされます。したがって、このレジスターへの書き込みは、DMA転送をセットアップする最後の手順である必要があります。

注: WR_DMA_LAST_PTR が WR_TABLE_SIZE に近づいたら、必ず WR_TABLE_SIZE と等しい値で WR_DMA_LAST_PTR をプログラムしてください。そうすることで、最小のオフセット (この例では0xF000_0200) で最初のディスクリプターへのロールオーバーが確実に行われます。WR_DMA_LAST_PTR レジスターのプログラミングの詳細は、Write DMA Descriptor Controllerレジスター の項の WR_DMA_LAST_PTR の説明を参照してください。