インテルのみ表示可能 — GUID: ohu1498252139806

Ixiasoft

7.1.1. レジスターアクセスの定義

7.1.2. PCIコンフィグレーション・ヘッダー・レジスター

7.1.3. PCI Express機能構造

7.1.4. インテル定義のVSEC Capabilityヘッダー

7.1.5. Uncorrectable Internal Error Status (修正不可能な内部エラーステータス) レジスター

7.1.6. Uncorrectable Internal Error Mask (修正不可能な内部エラーマスク) レジスター

7.1.7. Correctable Internal Error Status (修正可能な内部エラーステータス) レジスター

7.1.8. Correctable Internal Error Mask (修正可能な内部エラーマスク) レジスター

10.5.1. ebfm_barwrプロシージャー

10.5.2. ebfm_barwr_immプロシージャー

10.5.3. ebfm_barrd_waitプロシージャー

10.5.4. ebfm_barrd_nowtプロシージャー

10.5.5. ebfm_cfgwr_imm_waitプロシージャー

10.5.6. ebfm_cfgwr_imm_nowtプロシージャー

10.5.7. ebfm_cfgrd_waitプロシージャー

10.5.8. ebfm_cfgrd_nowtプロシージャー

10.5.9. BFMコンフィグレーション・プロシージャー

10.5.10. BFM共有メモリー・アクセス・プロシージャー

10.5.11. BFMログおよびメッセージ・プロシージャー

10.5.12. Verilog HDL Formattingファンクション

インテルのみ表示可能 — GUID: ohu1498252139806

Ixiasoft

2.4. デザイン例のシミュレーション

図 17. 手順

- テストベンチ・シミュレーション・ディレクトリーの pcie_example_design_tb を変更します。

- 選択したシミュレーターでシミュレーション・スクリプトを実行します。下の表を参照してください。

- 結果を分析します。

| シミュレーター | 作業ディレクトリー | 説明 |

|---|---|---|

| ModelSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/mentor/ |

|

| VCS* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/synopsys/vcs |

|

| NCSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/cadence |

|

| Xcelium* Parallel Simulator | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/xcelium |

|

DMAテストベンチは、次のタスクを実行します。

- DUT Endpointの非バーストAvalon-MMマスター・インターフェイスを使用して、エンドポイント・メモリーに書き込みます。

- DUT Endpointの非バーストAvalon-MMマスター・インターフェイスを使用して、エンドポイント・メモリーから読み出します。

- shmem_chk_ok タスクを使用してデータを検証します。

- ホストメモリー内の PCIe* アドレス空間へのMRd要求を実行するようDMAコントローラーに指示して、Endpoint DMAコントローラーに書き込みます。

- ホストメモリー内の PCIe* アドレス空間へのMWr要求を実行するようDMAコントローラーに指示して、Endpoint DMAコントローラーに書き込みます。このMWrは、前のMRdからのデータを使用します。

- shmem_chk_ok タスクを使用してデータを検証します。

エラーが発生しなかった場合、「Simulation stopped due to successful completion」とシミュレーションがレポートします。

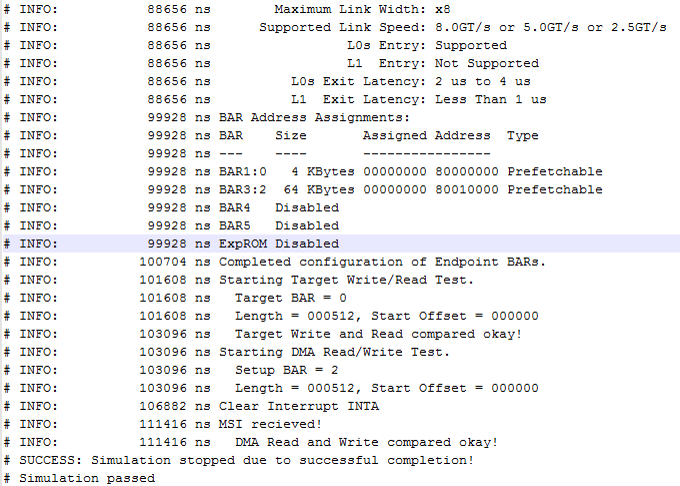

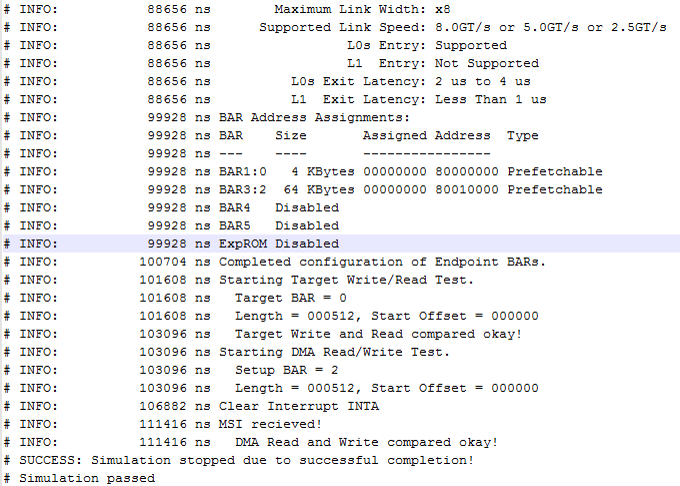

図 18. 成功したシミュレーション・テストベンチからの部分的なトランスクリプト