インテルのみ表示可能 — GUID: cju1541051426457

Ixiasoft

2.1. インテル® Stratix 10® エンベデッド・メモリー・ブロックにおけるバイトイネーブル

2.2. アドレス・クロック・イネーブルのサポート

2.3. 非同期クリアと同期クリア

2.4. メモリーブロックの誤り訂正コードのサポート

2.5. Force-to-Zero

2.6. コヒーレント読み出しメモリー

2.7. フリーズロジック

2.8. トゥルー・デュアル・ポート・デュアル・クロック・エミュレーター

2.9. インテル® Stratix 10® でサポートされているエンベデッド・メモリーIPコア

2.10. インテル® Stratix 10® エンベデッド・メモリーのクロッキング・モード

2.11. インテル® Stratix 10® エンベデッド・メモリーのコンフィグレーション

2.12. 読み出しアドレスレジスターおよび書き込みアドレスレジスターの初期値

インテルのみ表示可能 — GUID: cju1541051426457

Ixiasoft

5.1.2.1. シミュレーション結果

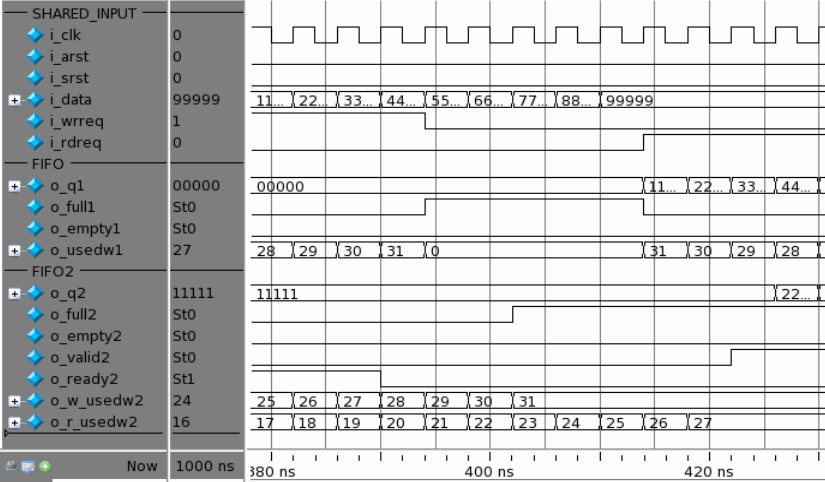

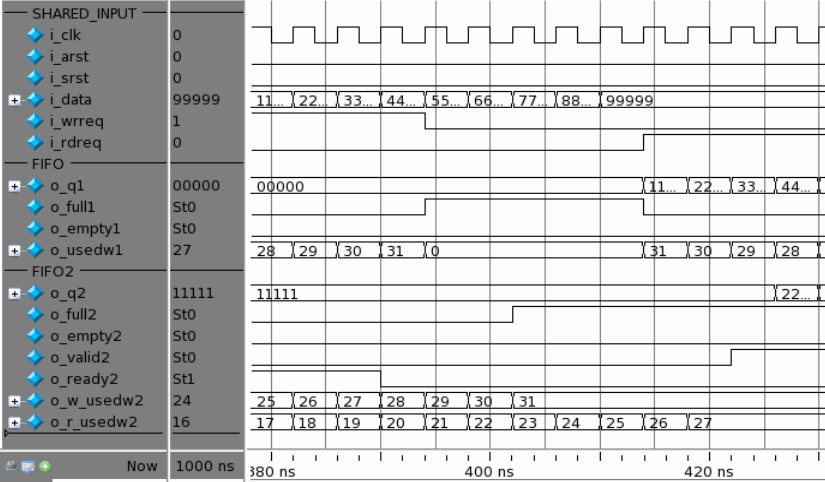

デザイン例のシミュレーション結果で示しているのは、FIFOとFIFO2 Intel FPGA IPコアの動作の比較です。

注: このデザイン例で使用されているFIFOとFIFO2 Intel FPGA IPコア両方の信号名の定義には、FIFOの入力ポートと出力ポートを参照します。

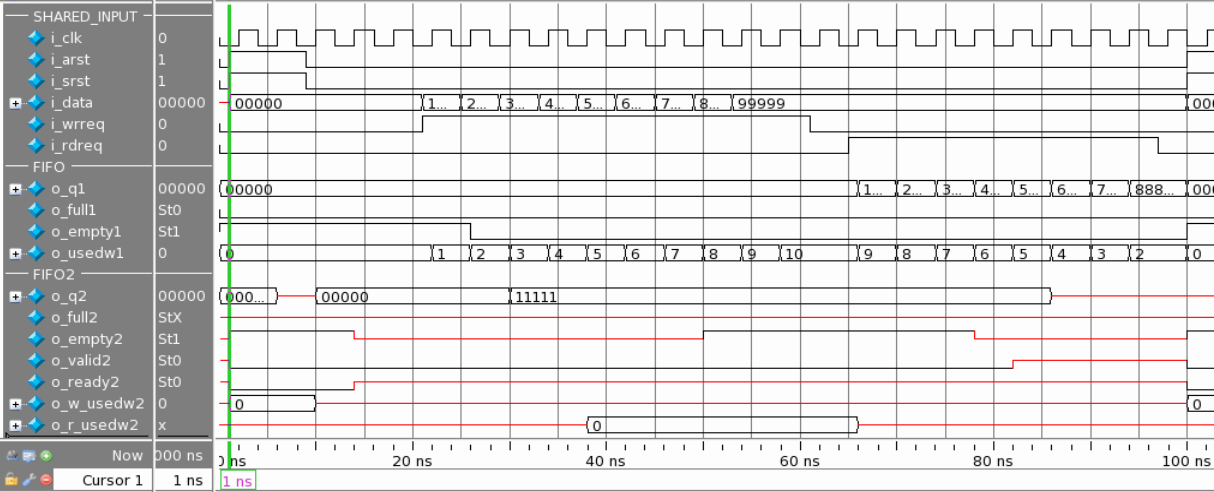

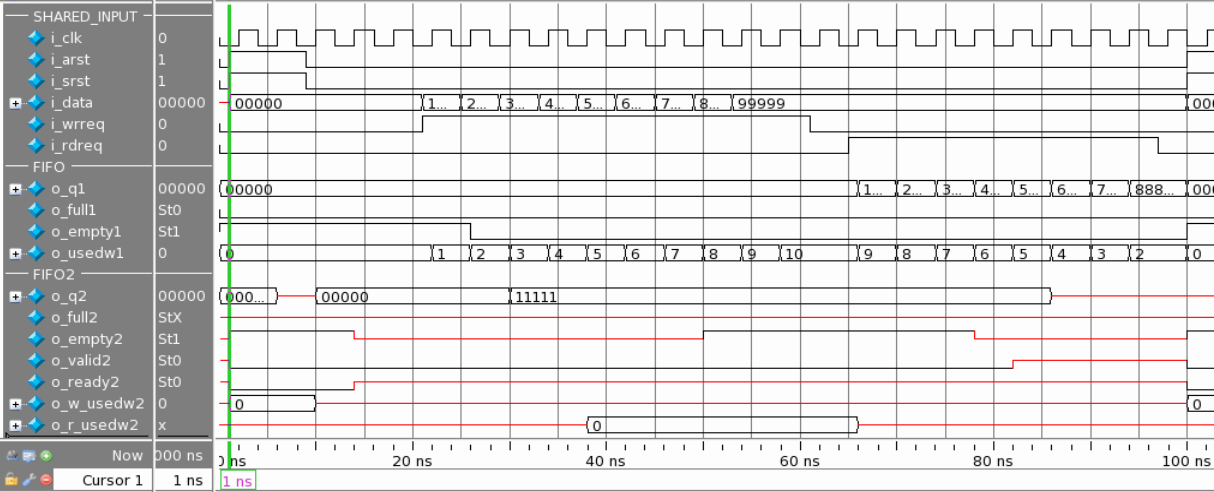

パート1 (0 - 100 ns)

シミュレーションのこのセクションで示すRead-after-Write動作では、FIFO2に対する無効なリセット条件を使用します。FIFO2に必要なリセット期間は32サイクルです。そのため、一部の信号では、2クロックサイクルのリセットだけでは既知の状態に戻ることができません。これが原因でFIFO2は想定どおりの動作ができなくなります。一方、FIFOでは正常なWrite-Then-Read動作が行われます。これは、FIFOで必要とされるのは、最低1クロックサイクルのリセットだけだからです。

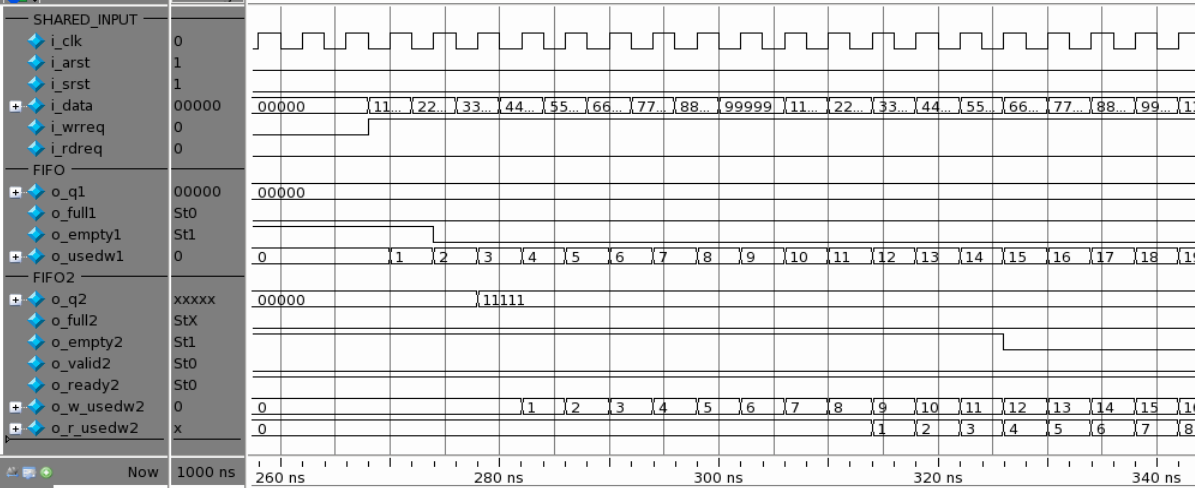

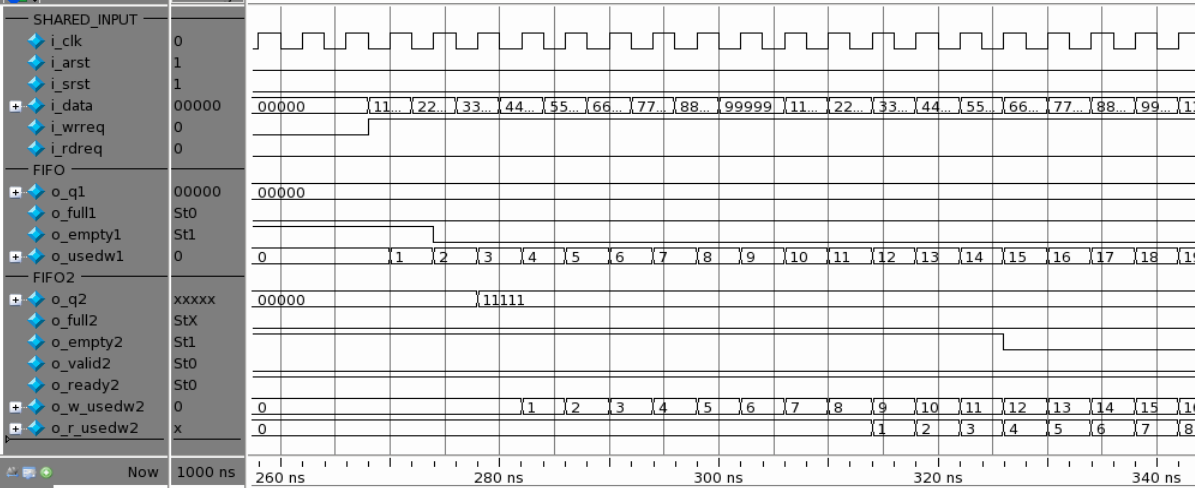

図 35. パート1 - FIFOのRead-after-write動作

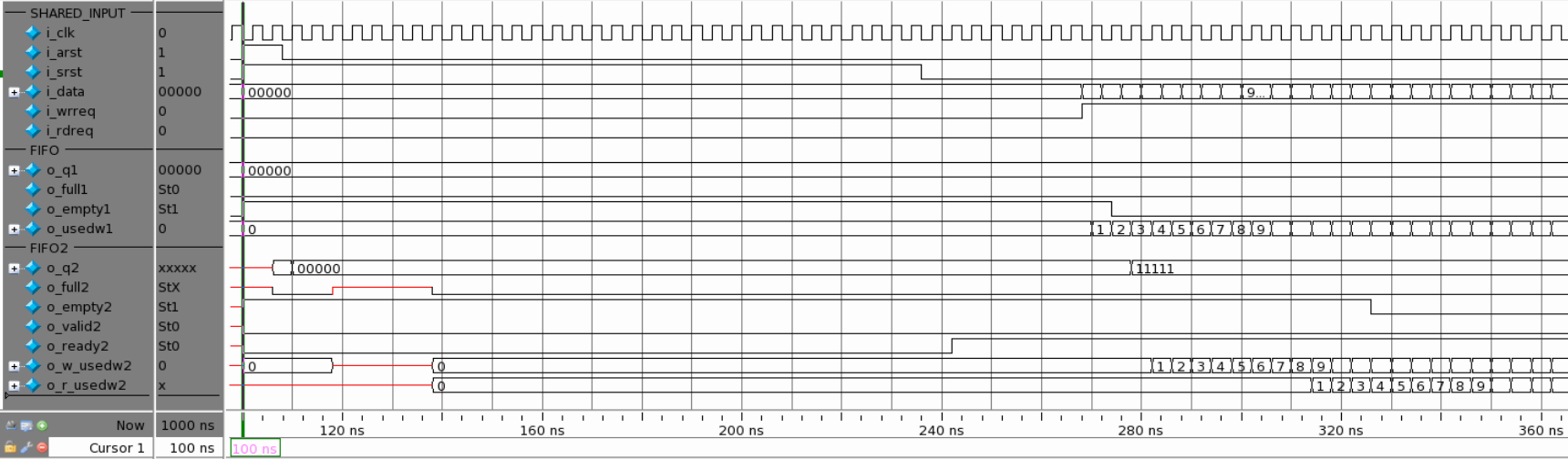

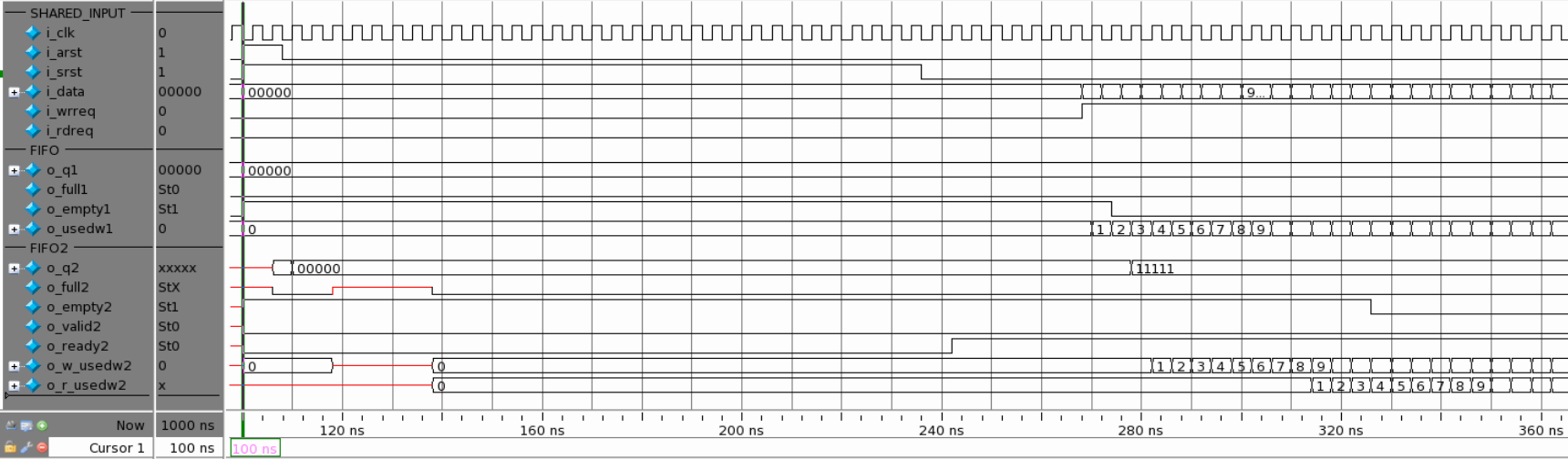

パート2 (100 - 480 ns)

シミュレーションのこのセクションで示すFIFO2動作では、有効なリセットスキームを使用し、その後にWrite-Then-Read動作を行います。32サイクルのリセット後、すべての信号が既知の状態に戻ります。また、8サイクルの待機が任意の操作の前に必要です。

図 36. パート2 - FIFO2の有効なリセットスキーム

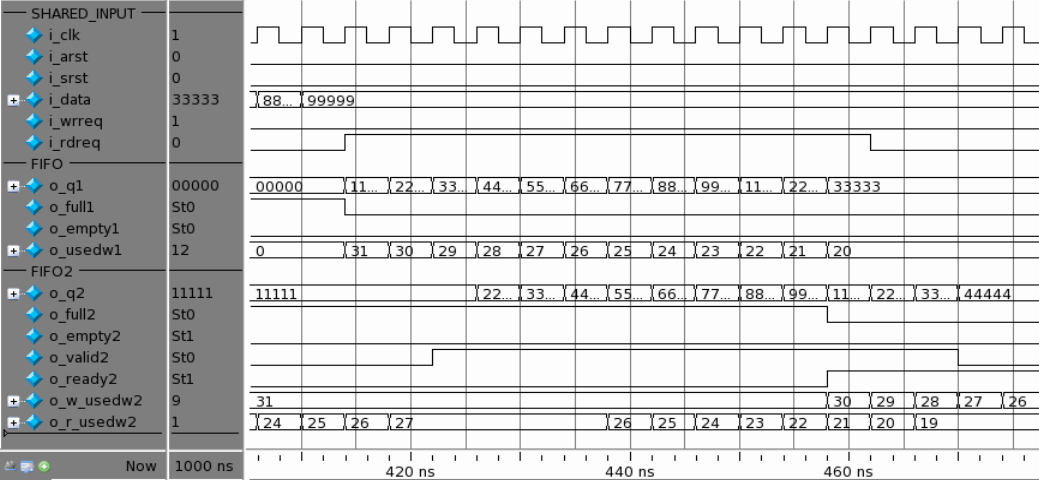

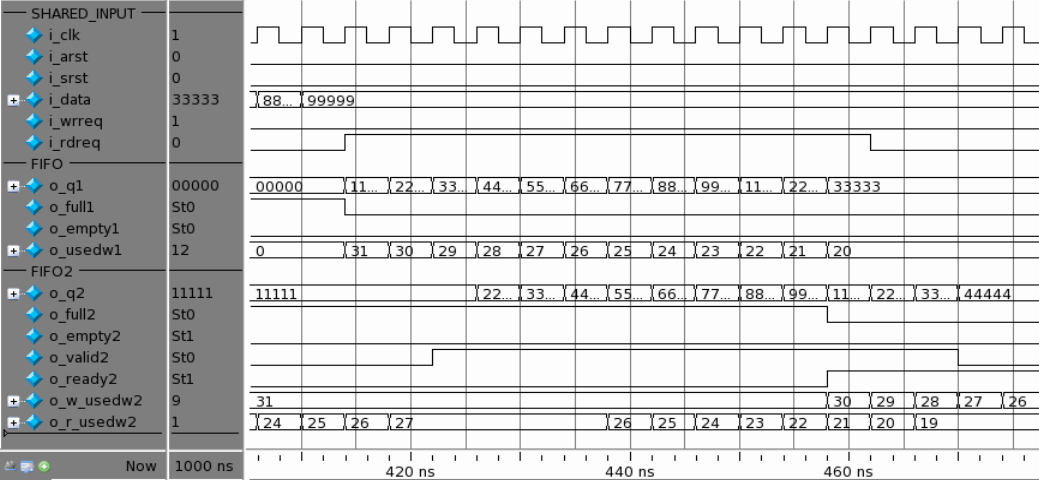

図 37. 書き込み動作

図 37 への注記 :

- usedw signal : 書き込み要求信号 (例えば i_wrreq ) がアサートされた後、 usedw 信号 (例えば o_usedw1 ) では、カウントが開始され、このときデータはFIFOに格納されます。FIFO2には usedw 信号が書き込み (例えば o_w_usedw2 ) と読み出し (o_r_usedw2) の両サイドにあります。書き込み usedw でのカウント開始は3サイクルの遅延後で、さらに8サイクルかけて読み出し usedw 信号が更新されます。

- Full and empty signals : FIFOフル信号 (例えば o_full1 ) がHighにアサートされるのは、FIFOのメモリーがフルになった後です。FIFO2フル信号 (例えば o_full2 ) がHighにアサートされるのは、 o_w_usedw2 信号と同じサイクルです。これによりメモリーがフルであることが示されます。注意が必要なのは、フル信号がアサートされる3サイクル前に ready 信号はすでにLowにアサートされ、これは想定されるFIFO2のパイプライン動作であるということです。FIFO空信号 (例えば o_empty1 ) は、1クロックサイクルのレイテンシーしかなく、Lowにアサートされるのは最初のデータがメモリーに書き込まれた後です。一方、FIFO2では3サイクルの遅延を取って、その空信号 (例えば o_empty2 ) が空でなくなったことを示します。これは、 o_r_usedw2 信号が1に上昇した後です。

図 38. 読み出し動作

図 38 への注記 :

- 読み出し動作では、FIFO o_usedw1 信号は、読み出し要求信号と同じ正のクロックエッジに反映されます。FIFO2の場合、2サイクルのレイテンシーが o_r_usedw2 信号に反映される前に観測されます。また、さらに9サイクルが o_r_usedw2 から o_w_usedw2 への伝播にかかります。

図 39. FIFOフル状態

図 39 への注記 :

- Ready signal : 有効なリセットスキームの後、FIFO2準備完了信号 (例えば o_ready2 ) はHighにアサートされ、これにより書き込み動作の準備ができたことが示されます。

注: FIFOにはこの信号はありません。

- Valid signal: FIFO有効信号 (例えば o_valid2 ) では、読み出されるデータが有効であることが示されます。有効な読み出し動作の場合、 o_valid2 信号がHighにアサートされるのは、2サイクルの遅延後で、読み出し要求 (例えば i_rdreq ) 信号のアサートを伴います。

注: FIFOにはこの信号はありません。

パート3 (480 - 700 ns)

シミュレーションのこのセクションでは、有効なリセット条件とそれに続くread-during-write動作について紹介します。リセット後、書き込み要求信号 (例えば i_wrreq ) がHighにアサートされます。数サイクル後、 i_rdreq 信号もHighにアサートされます。FIFOの場合、使用されているワード数はデータ読み出し中は維持され、これは想定される動作に従っています。この場合注意が必要なのは、FIFO2ではデータの読み出しは行われないということです。これは、 o_empty2 信号がLowにアサートされていないためで、FIFO2の有効な読み出し動作ではありません。

パート4 (700 ns以降)

シミュレーションのこのセクションでは、FIFOとFIFO2の動作の観察を異なるシナリオで行います。FIFO2 o_r_usedw2 信号でカウントダウンが2までされると、 o_empty2 信号がHighにアサートされ、内部チェックが行われます。2サイクル後、 o_empty2 信号が空でない状態に戻るのは、ステータスの検証後です。このメカニズムは、FIFO2用に特別にデザインされており、その多重パイプライン性に従っています。