インテルのみ表示可能 — GUID: dcf1541051368984

Ixiasoft

2.1. インテル® Stratix 10® エンベデッド・メモリー・ブロックにおけるバイトイネーブル

2.2. アドレス・クロック・イネーブルのサポート

2.3. 非同期クリアと同期クリア

2.4. メモリーブロックの誤り訂正コードのサポート

2.5. Force-to-Zero

2.6. コヒーレント読み出しメモリー

2.7. フリーズロジック

2.8. トゥルー・デュアル・ポート・デュアル・クロック・エミュレーター

2.9. インテル® Stratix 10® でサポートされているエンベデッド・メモリーIPコア

2.10. インテル® Stratix 10® エンベデッド・メモリーのクロッキング・モード

2.11. インテル® Stratix 10® エンベデッド・メモリーのコンフィグレーション

2.12. 読み出しアドレスレジスターおよび書き込みアドレスレジスターの初期値

インテルのみ表示可能 — GUID: dcf1541051368984

Ixiasoft

5.1.1. デザイン例の生成

- デザイン例をDesign Storeからダウンロードする。

- インテル® Quartus® Primeプロ・エディション開発ソフトウェアを使用してファイルを復元するには、Open Projectを選択して .par ファイルを選択します。 OKをクリックしてプロジェクトをロードします

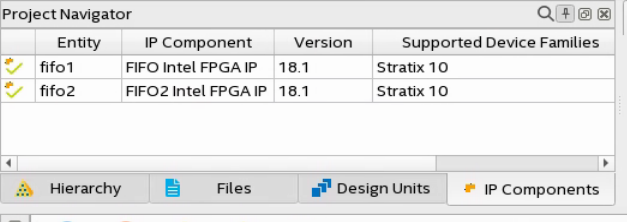

- プロジェクトが正常にロードされたらProject NavigatorウィンドウのIP componentタブに移動します。FIFO Intel FPGA IP コア (fifo1) をダブルクリックしてIP Parameter Editorを開き、IPコンフィグレーションを調べてFIFO IPファイルを再生成します。

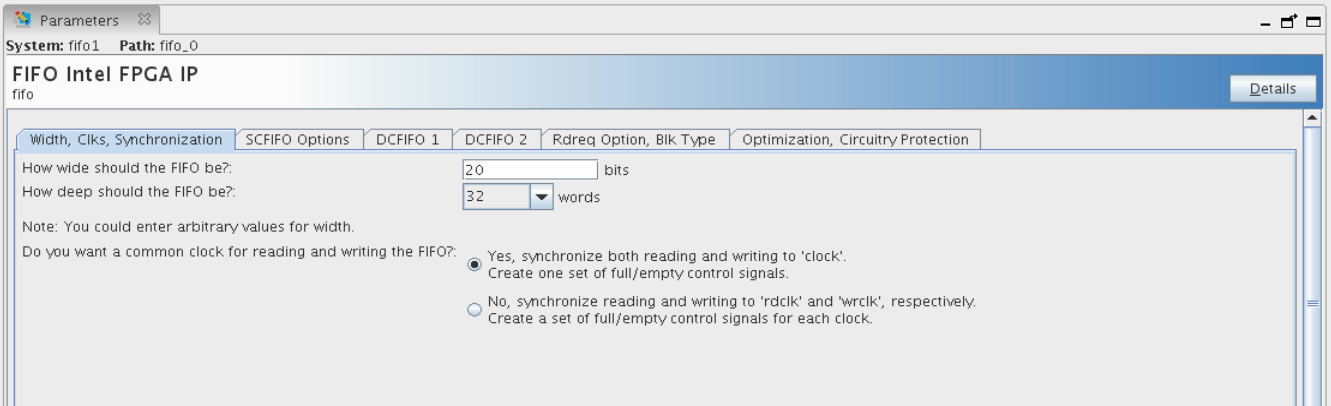

- IP Parameter Editorウィンドウで、次のパラメーターの設定が正しいか確認します。

パラメーター 値 How wide should the FIFO be? 20 bits How deep should the FIFO be? 32 words Read and Write Clock Single clock Signals full, empty, usedw[] Use Asynchronous Clear Yes Use Synchronous Clear Yes Memory Block Type MLAB FIFO mode Normal

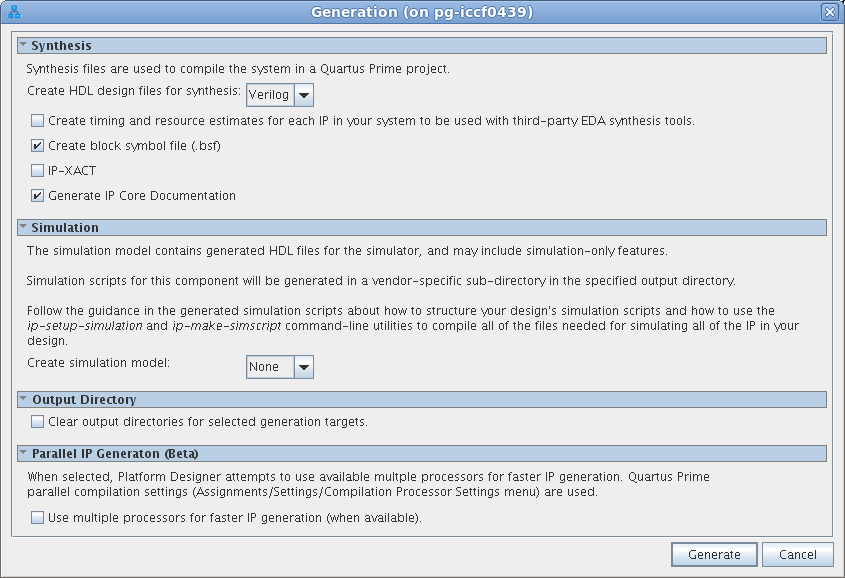

- このIPコアのHDLファイルを生成するには、Generate HDLをクリックします。 Generationダイアログボックスが表示されます。

- 出力ファイルの生成オプションを指定し、Generateをクリックします。合成ファイルおよびシミュレーション・ファイルが仕様に応じて生成されます。

- FIFO2 Intel FPGA IPコア (fifo2) の場合はステップ3から6までを繰り返し、IPコンフィグレーションを調べてFIFO2 IPファイルを再生成します。

- FIFOとFIFO2 Intel FPGA IP両方のHDLファイル生成が完了したら、Tools > Generate Simulator Setup Script for IPをクリックして複合シミュレーター・セットアップ・スクリプトを生成します。このスクリプトによって、FIFOおよびFIFO2 IPシミュレーションに必要なすべてのライブラリー・ファイルを自動入手します。デフォルトのディレクトリーを使用し、OKをクリックしてファイルを生成します。