インテルのみ表示可能 — GUID: nik1410564999828

Ixiasoft

インテルのみ表示可能 — GUID: nik1410564999828

Ixiasoft

10.1. トランシーバー・リコンフィグレーション・コントローラーIPコアの接続

トランシーバー・リコンフィグレーション・コントローラーIPコアはVシリーズのデバイスで利用可能で、IP CatalogのInterface Protocols/Transceiver PHYカテゴリーにあります。トランシーバー・リコンフィグレーション・コントローラーをインスタンス化すると、Enable offset cancellation blockおよびEnable PLL calibrationオプションがデフォルトでイネーブルされます。

トランシーバー・リコンフィグレーション・コントローラーIPコアのソフトウェア・ドライバーであるAltera PCIe Reconfig Driver IPコアは、Interface Protocols/PCIeのIP Catalogにおいても使用可能です。PCIe Reconfig Driverは、デザインが異なるリコンフィグレーション機能を必要とする場合に変更が可能なように、クリアテキストで実装されています。

この図が示すように、reconfig_to_xcvr[ <n> 70-1:0]バスとreconfig_from_xcvr[ <n> 46-1:0]バスは2つのコンポーネントを接続しています。100~125 MHzのフリーランニング・クロックをトランシーバー・リコンフィグレーション・コントローラーIPコアのmgmt_clk_clkクロック入力に提供する必要があります。

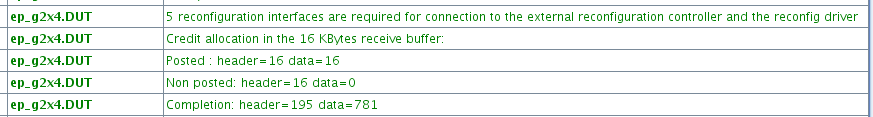

最初に、各レーンとTX PLLに個別のリコンフィグレーション・インターフェイスが必要となります。パラメーター・エディターは、この番号をメッセージ・ペインに表示します。この番号を控え、Transceiver Reconfiguration Controllerパラメーター・エディターのパラメーター値として入力する必要があります。次の図は、Gen2×4バリアントで報告されたメッセージを示しています。このバリアントには、各レーンに1つ、そしてTX PLLに1つの合計5つのインターフェイスを要します。

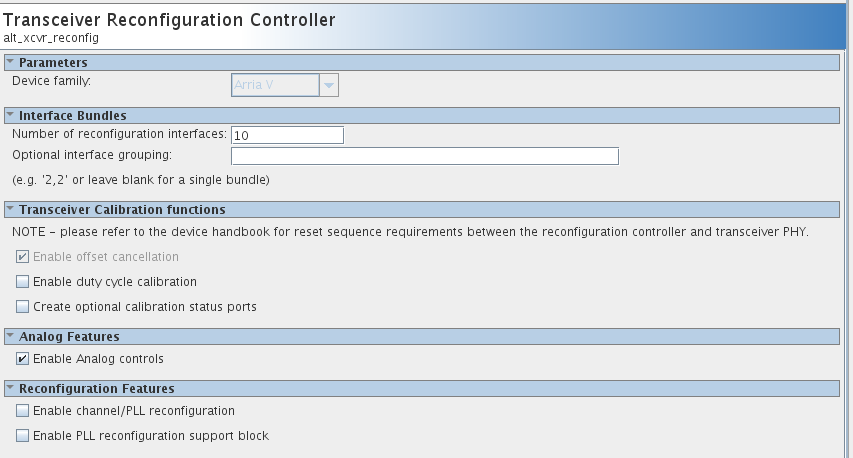

トランシーバー・リコンフィグレーション・コントローラーをインスタンス化する際、次の図が示すように必須のNumber of reconfiguration interfacesを指定する必要があります。

Transceiver Reconfiguration Controllerには、Optional interface groupingパラメーターが含まれています。トランシーバー・バンクは6個のチャネルを備えています。×4バリアントの場合、4レーンとTX PLLはすべて1つのバンク内に収まるため、特に特別なインターフェイスのグルーピングを必要としません。