インテルのみ表示可能 — GUID: mij1548189456191

Ixiasoft

インテルのみ表示可能 — GUID: mij1548189456191

Ixiasoft

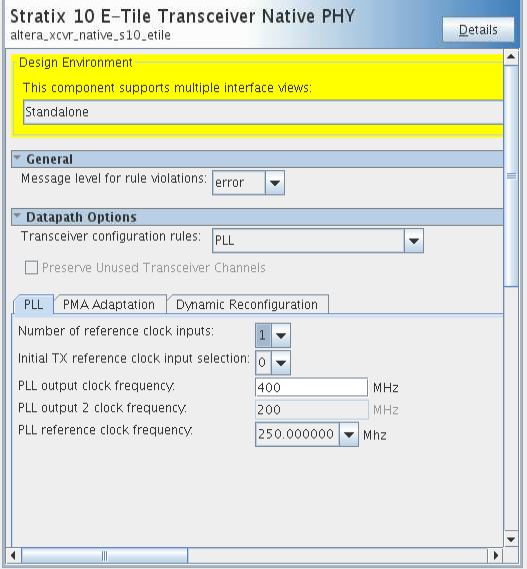

2.2.11. PLLモード

PLLモードは、Eタイル・トランシーバー・ネイティブPHY IPコアのコンフィグレーションです。これにより、Eタイル・トランシーバーをPLLとしてコンフィグレーションします。PLLモードは、外部EMIBクロッキング・コンフィグレーションに使われます ( 25Gbps PMA Directチャネル x 4 (FECオン、シングルFECブロック内 ) のユースケースを参照してください)。PLLと他のトランシーバー・コンフィグレーション・ルール間のダイナミック・リコンフィグレーションはサポートしていません。

トランシーバー・チャネルは、PLLモードで使用した後は、通常のトランシーバー動作には使用できません。PLLモードのネイティブPHY IPコアの出力をそれぞれのトランシーバー入力に接続する必要があります。

| パラメーター | 値 | 説明 |

|---|---|---|

| Number of reference clock inputs | 1、2、3、4、5 | 必要なリファレンス・クロック数を指定します。ネイティブPHY IPコアによって提示されるクロック入力は最大5です。 |

| Initial TX reference clock input selection | リファレンス・クロック入力数に基づく | 最初に選択したPLLリファレンス・クロック入力を指定します。これは、複数のTXリファレンス・クロック入力を動的に切り替えるときに、このコンフィグレーションで使用する開始クロック入力の選択を示します。 |

| PLL output clock frequency | 100から1000MHz | PLL出力周波数をMHz単位で指定します。 |

| PLL output 2 clock frequency | PLLからの出力 pll_clkout2 周波数 = 0.5* pll_clkout1 周波数 |

出力2のPLL出力周波数をMHz単位で指定します。 |

| PLL reference clock frequency | デバイス・データシート を参照してください。 | PLLのリファレンス・クロック周波数を指定します。 |

rx_clkout と pll_clkout2 クロックは、相互に非同期 (位相関係なし) です。また、ネイティブPHY IPから出力される他のクロックに対しても非同期 (位相関係なし) です。この2つのクロック間でデータ転送を行うには、対策を講じる必要があります。

| ポート名 | 入力/出力 | クロックドメイン | 幅 | 説明 |

|---|---|---|---|---|

| pll_refclk0 pll_refclk1 pll_refclk2 pll_refclk3 pll_refclk4 |

入力 | 該当なし | 各チャネルで1ビット | PLLのリファレンス・クロックです。 |

| pll_locked | 出力 | reconfig_clk | 各チャネルで1ビット | PLLのロックステータス信号。PLLチャネルをトランシーバー・チャネルへのクロックソースとして外部EMIBクロッキングを介して使用する場合は次の手順を実行します。

|

| tx_serial_data | 出力 | 該当なし | 各チャネルで1ビット | tx_serial_data ポートを使用するのは、PLLチャネルの場所を割り当てる場合のみです。このポートは、データを送信するためのアクティブなポートではありません。9 |

| pll_clkout1 pll_clkout2 |

出力 | 該当なし | 各チャネルで1ビット | PLLからの出力 pll_clkout2 周波数 = 0.5* pll_clkout1 周波数 |

set_location_assignment HSSIXCVR_4T9A18 -to <path>|xcvr_native_s10_etile_0|g_xcvr_native_insts[0].ct3_xcvr_native_inst|inst_ct3_xcvr_channel|inst_ct3_hssi_xcvr