インテルのみ表示可能 — GUID: dbs1602275463306

Ixiasoft

インテルのみ表示可能 — GUID: dbs1602275463306

Ixiasoft

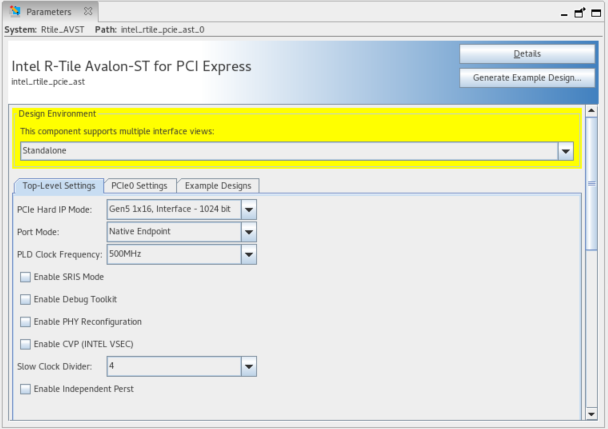

5.1. トップレベルの設定

| パラメーター | 値 | デフォルト値 | 説明 |

|---|---|---|---|

| Hard IP Mode | Gen5 1x16, Interface - 1024-bit Gen4 1x16, Interface - 1024-bit Gen3 1x16, Interface - 1024-bit Gen4 1x16, Interface - 512-bit Gen3 1x16, Interface - 512-bit Gen5 2x8, Interface - 512-bit Gen4 2x8, Interface - 512-bit Gen3 2x8, Interface - 512-bit Gen4 2x8, Interface - 256-bit Gen3 2x8, Interface - 256-bit Gen5 4x4, Interface - 256-bit Gen4 4x4, Interface - 256-bit Gen3 4x4, Interface - 256-bit Gen4 4x4, Interface - 128-bit Gen3 4x4, Interface - 128-bit PIPE Direct 16-channel |

Gen5 1x16, Interface - 1024-bit |

FPGAファブリックに実装されたトランザクション層とアプリケーション層の間のデータ・インターフェイスの幅、およびレーンレートを選択します。 次の要素を選択します。

レーンのデータレート:

レーン幅:

このコンフィグレーションの一部が使用可能なデバイスは、OPN番号の末尾にR2またはR3が付いているデバイスに限られます。詳細については、ポートあたりのAvalon Streamingインターフェイスのデータおよびヘッダーバス幅を参照してください。 |

| Port Mode | Native Endpoint Root Port Downstream Upstream |

Native Endpoint |

ポートタイプを指定します。

注:

IPをTLPバイパスモードで操作するには、DownstreamまたはUpstream Port Modeのいずれかを選択します。 |

| Enable PHY Reconfiguration | True/False | False | PHYリコンフィグレーション・インターフェイスをイネーブルします。

注: このパラメーターは、 インテル® Quartus® Primeの22.3リリースではイネーブルしないでください。

|

| PLD Clock Frequency | 500 MHz 475 MHz 450 MHz 425 MHz 400 MHz 300 MHz 275 MHz 250 MHz |

500 MHz (Gen5モードの場合) 500 MHz/300 MHz (Gen4およびGen3モードの場合、デフォルトの周波数は、IPがダブル幅モードかシングル幅モードかによって異なります) |

アプリケーション・クロックの周波数を選択します。使用可能なオプションは、Hard IP Modeパラメーターの設定によって異なります。 Gen5モードの場合、使用可能なクロック周波数は、500 MHz / 475 MHz / 450 MHz / 425 MHz / 400 MHzです。 Gen4およびGen3モードの場合、使用可能なクロック周波数は、IPがダブル幅モードかシングル幅モードかによって異なります。詳細については、IPからFPGAファブリックへのインターフェイスの概要を参照してください。 |

| Enable SRIS Mode | True/False | False | 独立したスペクトラム拡散クロック機能を使用した個別のリファレンス・クロック (SRIS) をイネーブルします。 |

| Enable CVP (INTEL VSEC) | True/False | False | このパラメーターを設定すると、CVPが単一のタイルに対してのみイネーブルされます。 |

| Slow Clock Divider | 2 4 |

4 | slow_clk を設定して、coreclkout_hip を2または4で割るようにすることができます。 |

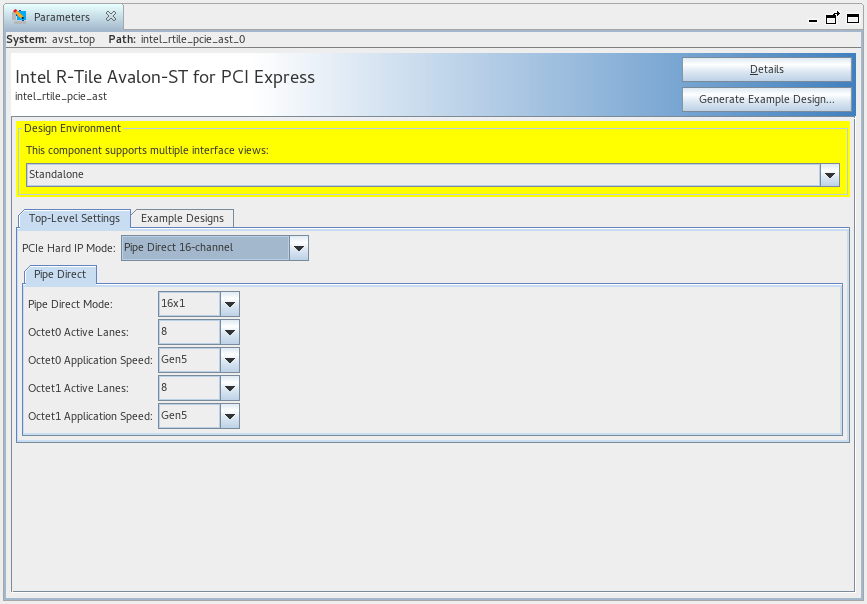

| PIPE Direct Mode | 1x16 2x8 4x4 8x2 2x4 / 1x8 4x2 / 1x8 8x1 / 1x8 1x8 / 2x4 4x2 / 2x4 8x1 / 2x4 1x8 / 4x2 2x4 / 4x2 8x1 / 4x2 1x8 / 8x1 2x4 / 8x1 4x2 / 8x1 16x1 |

16x1 | このオプションでは、トポロジーに基づき、レーン間のTXデスキューをグループごとに行います。 例えば、2x8トポロジーを選択した場合、EMIBのデスキューは、8つのEMIBチャネルごとに行われます。これにより、2セットのデスキューマーカー、デスキューエラーなどが発生します。 |

| Octet 0 Active Lanes | Off 1 2 3 4 5 6 7 8 |

8 | レーン0 ~ 7をイネーブルします。このパラメーターは、ユーザー・アプリケーション・ロジックで使用される下位レーンの数を示します。 |

| Octet 1 Active Lanes | Off 1 2 3 4 5 6 7 8 |

8 | レーン8 ~ 15をイネーブルします。このパラメーターは、ユーザー・アプリケーション・ロジックで使用される上位レーンの数を示します。 |