インテルのみ表示可能 — GUID: aem1602789221139

Ixiasoft

インテルのみ表示可能 — GUID: aem1602789221139

Ixiasoft

4.3.1.1. Avalon® Streaming RXおよびTXインターフェイスのTLPヘッダーとデータ・アライメント

TLPプリフィクス、ヘッダー、およびデータの送受信は、 Avalon® Streaming TXおよびRXインターフェイスで行われます。4つの Avalon® Streaming TX/RXインターフェイスがあり、4つのPCIeコアに対応しています。これらのインターフェイスの信号名に付けられるプリフィクスは、x16コアの場合は「p0」、x8コアの場合は「p1」、x4_0コアの場合は「p2」、x4_1コアの場合は「p3」 です。

これらの各インターフェイスには、最大4つのセグメントを含めることができます。このセグメントの信号名の表記は、*_st0_*、*_st1_*、*_st2_*、*_st3_* で表記されます。

パケットの開始 (SOP) シンボルは、パケットの開始を画定します。TLPは、データの有無にかかわらず、End of Packet (EOP) シンボルで終了します。EOP は、st0、st1、st2、またはst3セグメントで発生する場合、data valid = 1の最後のデータが対応するデータバス上にあることを意味します。

TLPは、データがない場合は、ヘッダー有効インジケーターによって修飾され、データがある場合は、データ有効インジケータによって修飾されます。TLPプリフィクスを修飾するためのプリフィクス有効インジケーターもあります。

Pタイルとの下位互換性のためにグローバル有効信号が必要な場合、データ有効との論理和を取ったヘッダーにより、グローバル有効インジケーターが提供されます。

この定義の目的は、パイプライン化されたヘッダー/プリフィクスとデータの転送をイネーブルして、帯域幅の目標値を達成することです。例えば、あるTLPのデータを転送している間に、次のTLPのヘッダーとプリフィクスを転送することができます。

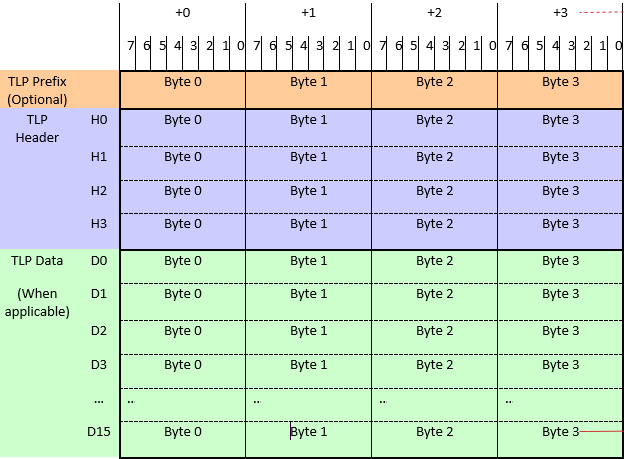

Avalon® ストリーミング・ヘッダーおよびTLPプリフィクス・ バス・パケット・フォーマットは、メモリー、コンフィグレーション、およびメッセージTLPのPCIe仕様で定義されているTLPパケット・フォーマットに従います。詳細については、TLPプリフィクス、ヘッダー、およびデータ (PCIe Header Formatチェックボックスがディスエーブルの場合) およびTLPプリフィクス、ヘッダー、およびデータ (PCIe Header Formatチェックボックスがイネーブルの場合) を参照してください。

RタイルのParameter EditorにあるPCIe Header format (PCIe Avalon® Settingsタブ内) というラベルが付いているチェックボックスを使用して、ヘッダーがビッグ・エンディアン形式とリトル・エンディアン形式のどちらに従うかを指定できます。このチェックボックスがイネーブルされていない場合は、ヘッダーはリトル・エンディアン形式に従います (TLPプリフィクス、ヘッダー、およびデータ (PCIe Header Formatチェックボックスがディスエーブルの場合) を参照してください。(この図で示しているプリフィクス、ヘッダー、およびデータは、インターフェイス全体ではなく、 Avalon® Streamingインターフェイスの1つのセグメントに対するものであることに注意してください)。

PCIe Header format チェックボックスがイネーブルされている場合、ヘッダーはビッグ・エンディアン形式に従います (TLPプリフィクス、ヘッダー、およびデータ (PCIe Header Formatチェックボックスがイネーブルの場合)) を参照してくだい。

| コンフィグレーション | リンクレート | 幅モード | ヘッダー | データ | アプリケーション・クロック周波数 (MHz) |

|---|---|---|---|---|---|

| 1x16 | Gen5 | ダブル幅 | st3_hdr[127:0] st2_hdr[127:0] st1_hdr[127:0] st0_hdr[127:0] |

st3_data[255:0] st2_data[255:0] st1_data[255:0] st0_data[255:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

| Gen4 | ダブル幅 | st3_hdr[127:0] st2_hdr[127:0] st1_hdr[127:0] st0_hdr[127:0] |

st3_data[255:0] st2_data[255:0] st1_data[255:0] st0_data[255:0] |

250MHz 275MHz 300MHz |

|

| シングル幅 7 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[255:0] st0_data[255:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

||

| Gen3 | ダブル幅 | st3_hdr[127:0] st2_hdr[127:0] st1_hdr[127:0] st0_hdr[127:0] |

st3_data[255:0] st2_data[255:0] st1_data[255:0] st0_data[255:0] |

250MHz 275MHz 300MHz |

|

| シングル幅 7 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[255:0] st0_data[255:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

||

| 2x8 | Gen5 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[255:0] st0_data[255:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

| Gen4 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[255:0] st0_data[255:0] |

250MHz 275MHz 300MHz |

|

| シングル幅 7 | st0_hdr[127:0] | st0_data[255:0] | 400MHz 425MHz 450MHz 475MHz 500MHz |

||

| Gen3 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[255:0] st0_data[255:0] |

250MHz 275MHz 300MHz |

|

| シングル幅 7 | st0_hdr[127:0] | st0_data[255:0] | 250MHz 275MHz 300MHz |

||

| 4x4 | Gen5 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[127:0] st0_data[127:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

| Gen4 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[127:0] st0_data[127:0] |

400MHz 425MHz 450MHz 475MHz 500MHz |

|

| シングル幅 7 | st0_hdr[127:0] | st0_data[127:0] | 400MHz 425MHz 450MHz 475MHz 500MHz |

||

| Gen3 | ダブル幅 | st1_hdr[127:0] st0_hdr[127:0] |

st1_data[127:0] st0_data[127:0] |

250MHz 275MHz 300MHz |

|

| シングル幅 7 | st0_hdr[127:0] | st0_data[127:0] | 250MHz 275MHz 300MHz |

- Configuration Mode 0 (1x16) の場合、TLPのSOPが発生するのは、セグメント0 (st0) またはセグメント2 (st2) のみです (つまり、所定のTLPはセグメント1またはセグメント3では開始できません)。

- ダブル幅モードのConfiguration Mode 0 (1x16) の場合、セグメント2 (st2_hdr) のヘッダーが許可されるのは、セグメント0 とセグメント1も使用している場合のみです (つまり、st0_hdr、st1_hdrおよびst0_data、st1_dataも使用している場合です)。

- シングル幅モードのConfiguration Mode 0 (1x16) では、クロックサイクルごとに 1つのセグメント (つまり、st0_hdr/st0_dataまたは st1_hdr/st1_data) しか使用できません。さらに、セグメント1を使用している場合、st0_dataは前のTLPで使用する必要があります。