インテルのみ表示可能 — GUID: psj1612899669712

Ixiasoft

インテルのみ表示可能 — GUID: psj1612899669712

Ixiasoft

4.3.7. コンフィグレーション・インターセプト・インターフェイス

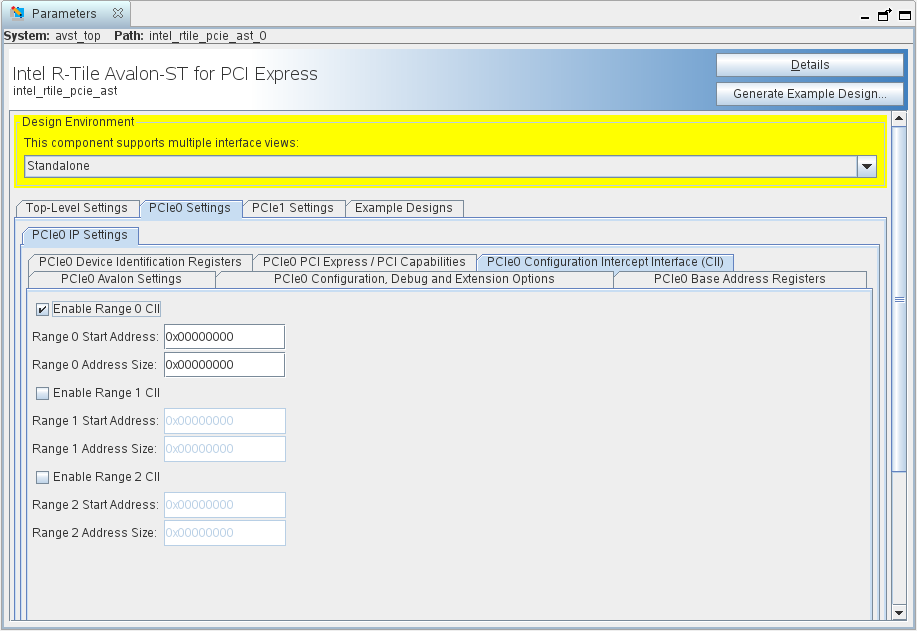

コンフィグレーション・インターセプト・インターフェイス (CII) を使用すると、アプリケーション・ロジックにより、リンク上のコンフィグレーション (CFG) リクエストの発生を検出し、そのビヘイビアを変更することが可能です。さらに柔軟性を持たせるために、PCI Express向けRタイルインテルFPGA IPを使用すると、このインターフェイスを使用して、インターセプトするPCIeコンフィグレーション・スペース範囲を最大3つ定義することが可能です ( IP Parameter EditorのCIIアドレス範囲を参照してください。許可される範囲は0x ~ 0xFFFです)。

アプリケーション・ロジックによるCFGリクエストの検出は、cii_req_o の立ち上がりエッジでされます。EMIBのレイテンシーのため、cii_req_o のデアサートは、cii_halt_i のデアサートの何サイクルも後にされる可能性があります。

アプリケーション・ロジックでは、CIIを使用して次のことを実行可能です。

- コントローラーによるCFGリクエストの処理を遅らせます。これにより、アプリケーションでは、最初にハウスキーピング・タスクを実行できます。

- CfgWrリクエストのデータペイロードを上書きします。アプリケーション・ロジックでは、CfgRdコンプリーションTLPのデータペイロードの上書きもできます。

このインターフェイスを使用すると、Intel Vendor Specific Extended Capability (VSEC) レジスターを実装することもできます。Intel VSECレジスター (アドレス0xD00から0xFFF) をターゲットとするすべてのコンフィグレーション・アクセスは、このインターフェイスに自動でマッピングされ、このインターフェイスを介して監視できます。

このインターフェイスを使用していない場合は、cii_halt_p0/1 をロジック0に接続します。

| 信号名 | 方向 | 説明 | EP/RP/BP | クロックドメイン |

|---|---|---|---|---|

| pX_cii_req_o | 出力 | CFGリクエストがインターセプトされ、他のすべてのCII信号が有効であることを示します。 | EP | slow_clk |

| pX_cii_hdr_poisoned_o | 出力 | CIIで受信したTLPヘッダーの有害なビットです。 | EP | slow_clk |

| pX_cii_hdr_first_be_o[3:0] | 出力 | CIIで受信したTLPヘッダーの最初のdwordバイト・イネーブル・フィールドです。 | EP | slow_clk |

| pX_cii_func_num_o[2:0] | 出力 | CIIで受信したTLPヘッダーのファンクション番号です。 | EP | slow_clk |

| pX_cii_wr_o | 出力 | cii_dout_p0/1 が有効であることを示します。この信号は、コンフィグレーション書き込みリクエストに対してのみアサートされます。 | EP | slow_clk |

| pX_cii_wr_vf_active_o | 出力 | 受信したTLPがコントローラー内の仮想ファンクション (VF) をターゲットにしていることを示します。これは、cii_vf_num_o[10:0] によって識別されます。 | EP | slow_clk |

| pX_cii_vf_num_o[10:0] | 出力 | ターゲットになったコントローラー内のVFを識別します。 | EP | slow_clk |

| pX_cii_addr_o[9:0] | 出力 | CIIで受信したTLPヘッダーのダブルワード・レジスター・アドレスです。 | EP | slow_clk |

| pX_cii_dout_o[31:0] | 出力 | リンクパートナーからアプリケーション・クライアントへの受信TLPペイロードデータです。データはリトル・エンディアン形式です。最初に受信したペイロードバイトはビット [7: 0] にあります。 | EP | slow_clk |

| pX_cii_override_en_i | 入力 | オーバーライド・イネーブルです。アプリケーション・ロジックによってこの入力をアサートすると、PCIeハードIPでは、CfgWrペイロードまたはCfgRdコンプリーションをオーバーライドします。このとき使用するデータは、cii_override_din_i[31:0] のアプリケーション・ロジックによって提供されます。 | EP | slow_clk |

| pX_cii_override_din_i[31:0] | 入力 | オーバーライド・データです。

|

EP | slow_clk |

| pX_cii_halt_i | 入力 | フロー・コントロール入力信号です。cii_halt_p0/1 がアサートされると、PCIeハードIPでは、PCIeコンフィグレーション・スペース・レジスターに対するCFGリクエストの処理を停止します。 | EP | slow_clk |