インテルのみ表示可能 — GUID: bgn1651172612535

Ixiasoft

1. PCI Express向けRタイル Avalon® Streamingインテル FPGA IPについて

2. IPアーキテクチャーおよび機能の説明

3. 高度な機能

4. インターフェイス

5. パラメーター

6. トラブルシューティング/デバッグ

7. PCI Express* 向けRタイル Avalon® StreamingインテルFPGA IPユーザーガイドのアーカイブ

8. PCI Express向けRタイル Avalon® Streaming インテルFPGA IPユーザーガイドの文書改訂履歴

A. コンフィグレーション・スペース・レジスター

B. ルートポートの列挙

C. エンドポイント・モードでのアドレス変換サービス (ATS) の実装

D. TLPバイパスモードでのユーザー・アプリケーションへのパケット転送

3.2.2.5.1. VirtIO Common Configuration Capability Register (アドレス: 0x012)

3.2.2.5.2. VirtIO Common Configuration BAR Indicator Register (アドレス: 0x013)

3.2.2.5.3. VirtIO Common Configuration BAR Offset Register (アドレス: 0x014)

3.2.2.5.4. VirtIO Common Configuration Structure Length Register (アドレス: 0x015)

3.2.2.5.5. VirtIO Notifications Capability Register (アドレス: 0x016)

3.2.2.5.6. VirtIO Notifications BAR Indicator Register (アドレス: 0x017)

3.2.2.5.7. VirtIO Notifications BAR Offset Register (アドレス: 0x018)

3.2.2.5.8. VirtIO Notifications Structure Length Register (アドレス: 0x019)

3.2.2.5.9. VirtIO Notifications Notify Off Multiplier Register (アドレス: 0x01A)

3.2.2.5.10. VirtIO ISR Status Capability Register Register (アドレス: 0x02F)

3.2.2.5.11. VirtIO ISR Status BAR Indicator Register (アドレス: 0x030)

3.2.2.5.12. VirtIO ISR Status BAR Offset Register (アドレス: 0x031)

3.2.2.5.13. VirtIO ISR Status Structure Length Register (アドレス: 0x032)

3.2.2.5.14. VirtIO Device Specific Capability Register (アドレス: 0x033)

3.2.2.5.15. VirtIO Device Specific BAR Indicator Register (アドレス: 0x034)

3.2.2.5.16. VirtIO Device Specific BAR Offset Register (アドレス0x035)

3.2.2.5.17. VirtIO Device Specific Structure Length Register (アドレス: 0x036)

3.2.2.5.18. VirtIO PCI Configuration Access Capability Register (アドレス: 0x037)

3.2.2.5.19. VirtIO PCI Configuration Access BAR Indicator Register (アドレス: 0x038)

3.2.2.5.20. VirtIO PCI Configuration Access BAR Offset Register (アドレス: 0x039)

3.2.2.5.21. VirtIO PCI Configuration Access Structure Length Register (アドレス: 0x03A)

3.2.2.5.22. VirtIO PCI Configuration Access Data Register (アドレス: 0x03B)

4.3.1. Avalon® Streamingインターフェイス

4.3.2. 精密時間測定インターフェイス (エンドポイントのみ)

4.3.3. 割り込みインターフェイス

4.3.4. ハードIPリコンフィグレーション・インターフェイス

4.3.5. エラー・インターフェイス

4.3.6. コンプリーション・タイムアウト・インターフェイス

4.3.7. コンフィグレーション・インターセプト・インターフェイス

4.3.8. パワー・マネジメント・インターフェイス

4.3.9. ハードIPステータス・インターフェイス

4.3.10. ページ・リクエスト・サービス (PRS) インターフェイス (エンドポイントのみ)

4.3.11. ファンクション・レベル・リセット (FLR) インターフェイス (エンドポイントのみ)

4.3.12. SR-IOV VFエラー・フラグ・インターフェイス (エンドポイントのみ)

4.3.13. 汎用VSECインターフェイス

5.2.3.1. Deviceの機能

5.2.3.2. VirtIOのパラメーター

5.2.3.3. Linkの機能

5.2.3.4. Legacy Interrupt Pin Register

5.2.3.5. MSI機能

5.2.3.6. MSI-Xの機能

5.2.3.7. Slotの機能

5.2.3.8. Latency Tolerance Reporting (LTR)

5.2.3.9. Process Address Space ID (PASID)

5.2.3.10. Device Serial Numberの機能

5.2.3.11. Page Request Service (PRS)

5.2.3.12. Access Control Service (ACS)

5.2.3.13. Power Management

5.2.3.14. Vendor Specific Extended Capability (VSEC) Register

5.2.3.15. TLP Processing Hints (TPH)

5.2.3.16. Address Translation Services (ATS) の機能

5.2.3.17. Precision Time Management (PTM)

インテルのみ表示可能 — GUID: bgn1651172612535

Ixiasoft

6.6.3. RタイルDebug Toolkitの起動

PCIe向けインテルRタイルAvalon Streaming IPに付属のデザイン例を使用して、RタイルDebug Toolkitの使用方法を理解することができます。PCI Expres向けRタイルAvalon StreamingインテルFPGA IPデザイン例ユーザーガイドに記載されている手順に従って、このデザイン例のSRAMオブジェクト・ファイル (.sof) を生成します。

RタイルDebug Toolkitを使用するには、Agilex Iシリーズ開発キットで.sofをプログラムします。その後、System Consoleを開き、デザインをSystem Consoleにロードします。.sofをSystem Consoleにロードすると、System Consoleによるデザインとの通信が、NPDMEユニットを使用してできるようになります。

次の手順に従って、タスクを完了します。

- インテル® Quartus® Primeプログラマーを使用して、.sofをインテルFPGA開発キットにダウンロードします。

注: 正常に動作させるには、 インテル® Quartus® Primeプロ・エディション開発ソフトウェアの完全インストールを使用してください。さらに、sofの生成に使用したものと同じバージョンの インテル® Quartus® Primeのプログラマーおよび インテル® Quartus® Primeプロ・エディション開発ソフトウェアのデバイスを使用してください。注: インテル® Quartus® Primeプロ・エディションProgrammer and Toolsのスタンドアロン・インストールは動作しませ ん。

- System Consoleにデザインをロードするには、次の手順に従います。

- インテル® Quartus® Primeプロ・エディション開発ソフトウェアを起動します。

- System Consoleを立ち上げます。それにはTools、System Debugging Tools、System Consoleの順に選択します。

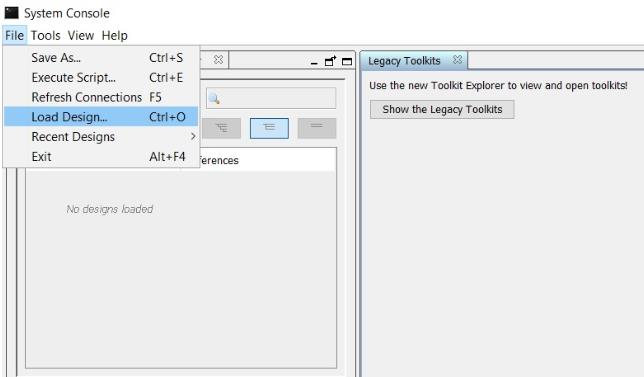

- System Console Fileメニューで、Load Designを選択し、.sofファイルを探します。

- .sofを選択し、OKをクリックします。.sofがSystem Consoleにロードされます。

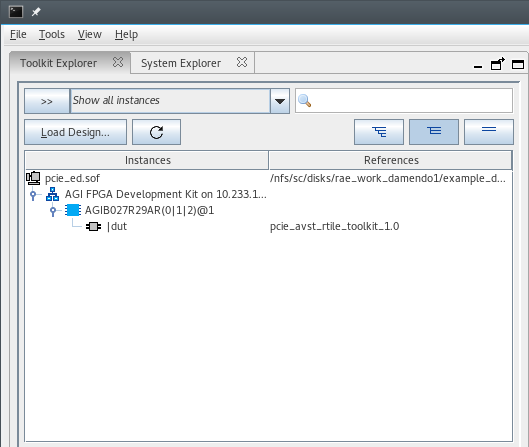

- System Console Toolkit Explorerウィンドウに、RタイルDebug ToolkitがイネーブルされているデザインにあるすべてのDUTが一覧表示されます。

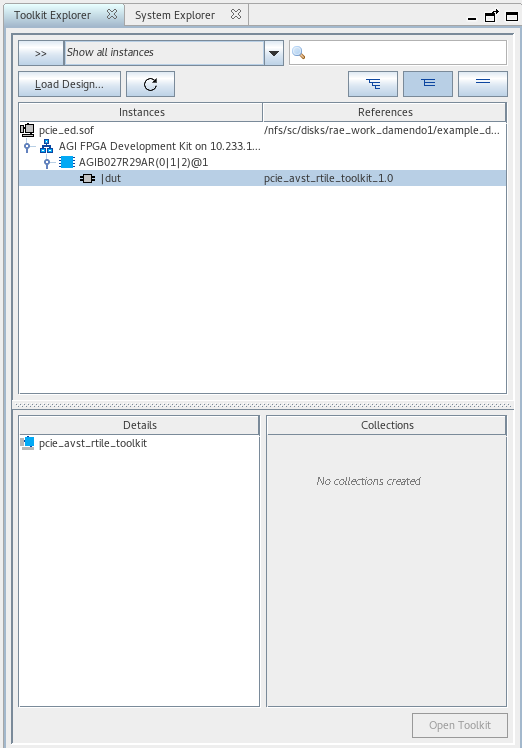

- Instances列の下で、RタイルDebug ToolkitがあるDUTを選択します。そうすると、選択したDUTのDebug ToolkitインスタンスがDetailsウィンドウに表示されます。

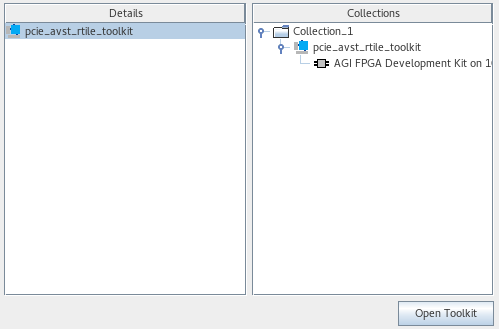

- pcie_avst_rtile_toolkitをDetailsパネルで選択します。

- Open Toolkitをクリックすると、Toolkitのインスタンスが開きます。

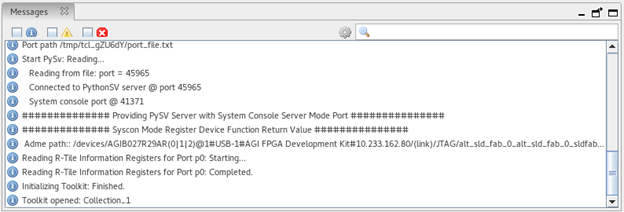

- Debug Toolkitの初期化とロードが行われると、Messagesウィンドウに次のようなメッセージが表示されます。

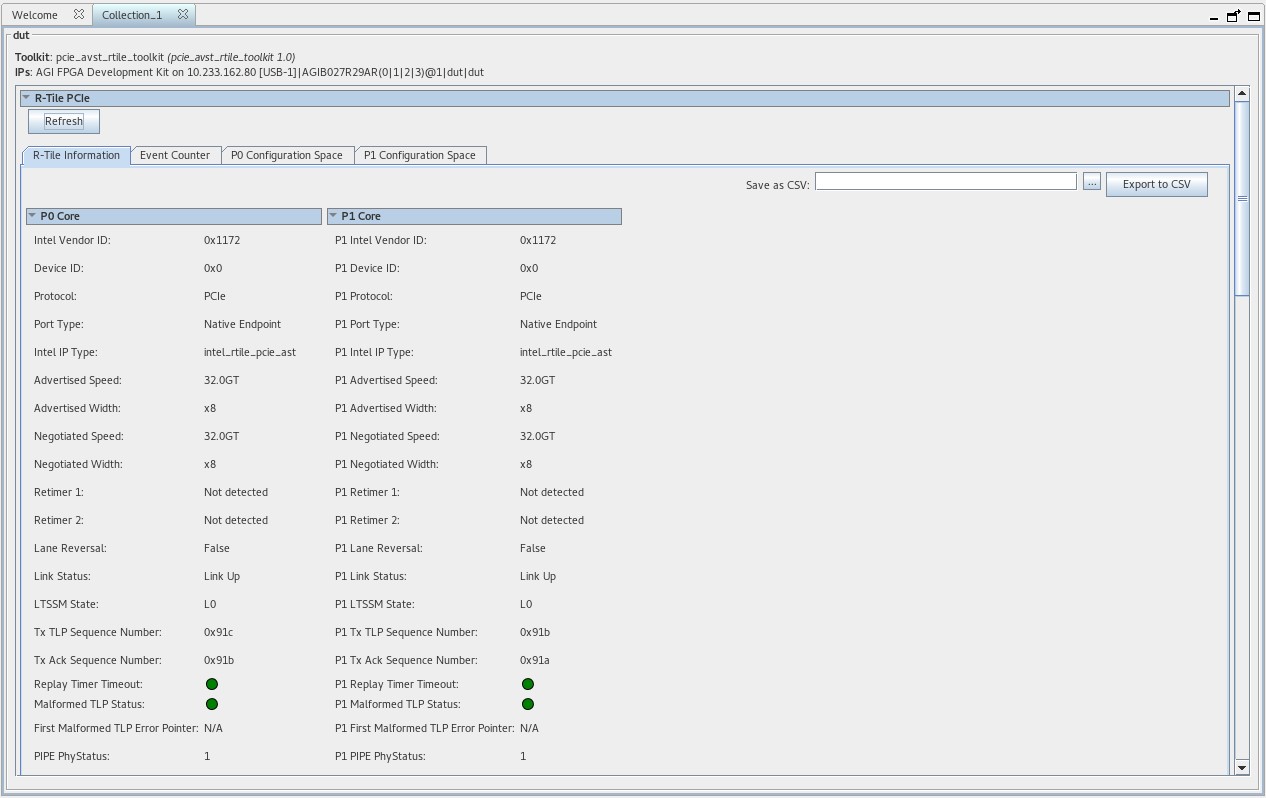

- 新しいウィンドウが開き、RタイルPCIe Toolkitのメインビューが表示されます。

- Instances列の下で、RタイルDebug ToolkitがあるDUTを選択します。そうすると、選択したDUTのDebug ToolkitインスタンスがDetailsウィンドウに表示されます。