インテルのみ表示可能 — GUID: jwf1650905924998

Ixiasoft

インテルのみ表示可能 — GUID: jwf1650905924998

Ixiasoft

6.6.1. 概要

RタイルDebug Toolkit (DTK) は、Rタイル用のシステム・コンソール・ベースのツールです。これにより、PCIeリンクのリアルタイム制御、監視、およびデバッグを行うことができます。

- IPコンフィグレーションおよびリンクステータスを監視します。

- PCIeコンフィグレーション・スペースを監視します。

- エラーとイベントの状態について、さまざまなカウンターを監視します。

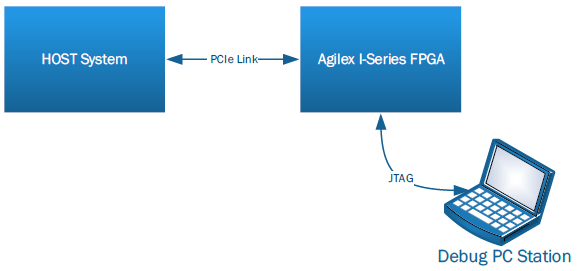

- Host: リンク・パートナー・コンポーネント。PCIeリンクを介してRタイルに接続しています。

- Agilex I-Series FPGA: このコンポーネントには、デバッグ中のRタイルPCIe IPが含まれています。

- Debug PC Station: 追加コンピュータシステム。Debug Toolkitを実行する インテル® Quartus® Primeプロ・エディション開発ソフトウェアがインストール済みで、JTAG接続でAgilex IシリーズFPGAに接続しています。

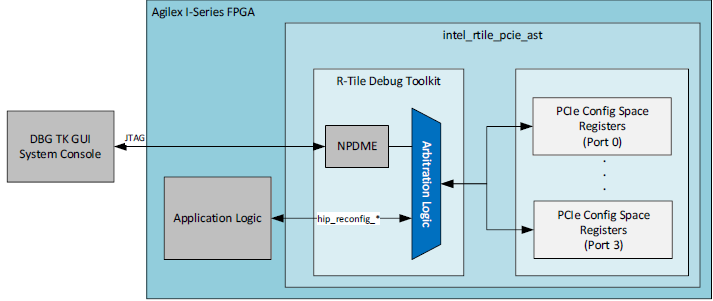

RタイルDebug Toolkitをイネーブルすると、生成されたIPの intel_pcie_ftile_ast モジュールには、Debug Toolkitモジュールと関連ロジックが含まれます。これについては、Debug Toolkitのアービトレーション で示しています。

デバッグPCステーションは、System Consoleツールを実行している場合、Native PHY Debug Master Endpoint (NPDME) を介してDebug Toolkitに接続されます。この接続は、インテルFPGAダウンロード・ケーブルを介し、JTAGを使用して行われます。

RタイルDebug ToolkitをIP Parameter Editorでイネーブルすると、ハードIPリコンフィグレーション・インターフェイスがイネーブルされます。マルチプレクサが実装され、アプリケーション・ロジックとDebug Toolkitの間のダイナミック切り替えが可能です。アプリケーション・ロジックは、デフォルトのアクセス権を持っています。System ConsoleツールでDebug Toolkitを起動すると、アービトレーションのが自動的に選択されます。DTKがSystem Consoleで開いている間は、アプリケーション・ロジックによるハードIPリコンフィグレーション・インターフェイス上での信号の駆動はできません。System ConsoleのDebug Toolkitウィンドウを閉じると、アプリケーション・ロジックによるハードIPリコンフィグレーション・インターフェイスの駆動が再び可能になります。

進行中のトランザクションがないことを確認するための措置として、Debug Toolkitが正常に起動できるのは、アプリケーション・ロジックによって行われた保留中の読み出しまたは書き込みトランザクションが、ハードIPリコンフィグレーション・インターフェイス上に存在しない場合のみです。