インテルのみ表示可能 — GUID: pdo1638456111011

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: pdo1638456111011

Ixiasoft

4.5.1.1.2. ソフトウェア・デザインフロー

この項では、 Nios® Vプロセッサー・ソフトウェア・プロジェクトを生成および構築するためのデザインフローを提供します。ビルドフローを合理化するために、デザイン・プロジェクトで同様のディレクトリー・ツリーを作成することをお勧めします。ソフトウェア・デザインフローは、このディレクトリー・ツリーに基づいています。

次の手順を使用して、ソフトウェア・プロジェクトのディレクトリー・ツリーを作成します。

- デザイン・プロジェクト・フォルダーに、software というフォルダーを作成します。

- software フォルダーに、app および bsp という2つのフォルダーを作成します。

図 23. ソフトウェア・プロジェクトのディレクトリー・ツリー

BSPプロジェクト・アプリケーションの作成

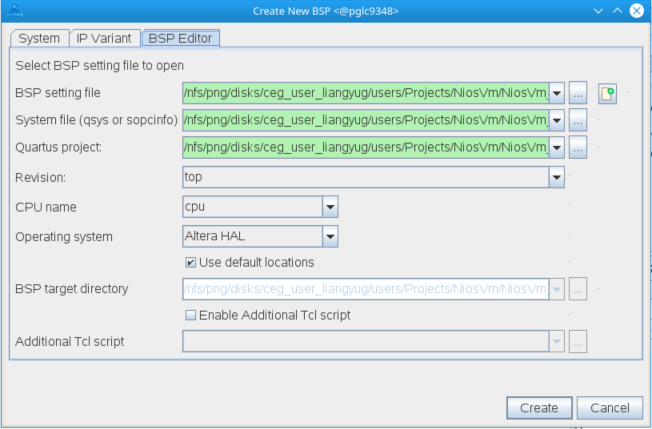

選択した Nios® Vプロセッサーのブートオプションに従って、BSPエディターの設定を編集する必要があります。

BSP Editorを起動するには、次の手順を実行します。

- Platform Designerウィンドウで、File > New BSPを選択します。Create New BSPウィンドウが表示されます。

- BSP setting fileでは、software/bsp フォルダーに移動し、BSPに settings.bsp という名前を付けます。

BSPパス: <project directory>/software/bsp/settings.bsp

- System file (qsys or sopcinfo) では、Nios V/m processor Platform Designerシステム (*.qsys) を選択します。

- Quartus projectでは、Quartus Project Fileを選択します。

- Revisionでは、正しいリビジョンを選択します。

- CPU nameでは、Nios V/mプロセッサーを選択します。

- Operating systemでは、Altera HALを選択します。

- Createをクリックして、BSPファイルを作成します。

図 24. Create New BSPウィンドウ

BSP EditorのコンフィグレーションおよびBSPプロジェクトの生成

- BSP Editorで、BSP Linker Scriptをクリックします。

- Linker Section Nameで、次の設定を実行します。

- Linker Region Nameで、.text をQSPIフラッシュに設定します。

- デザインの好みに応じて、.exceptions をOCRAM/ External RAMまたはQSPI Flashに設定します。

- 残りの項目をOCRAMまたは外部RAMに設定します。

図 25. ExceptionsがOCRAM/外部RAMに設定されている場合のリンカー領域の設定図 26. ExceptionsがQSPIフラッシュに設定されている場合のリンカー領域の設定 - Main > Settings > Advanced > hal.linkerに移動します。

- 例外がOCRAMまたはExternal RAMに設定されている場合は、次をイネーブルします。

- allow_code_at_reset

- enable_alt_load

- enable_alt_load_copy_rodata

- enable_alt_load_copy_rwdata

- enable_alt_load_copy_exceptions

図 27. 例外エージェントOCRAMまたは外部RAMのhal.linker設定 - 例外がQSPIフラッシュに設定されている場合は、次をイネーブルします。

- allow_code_at_reset

- enable_alt_load

- enable_alt_load_copy_rodata

- enable_alt_load_copy_rwdata

図 28. QSPIフラッシュのhal.linker設定 - Generate BSPをクリックします。BSPの生成が成功したことを確認します。

- BSP Editorを閉じます。

アプリケーション・プロジェクト・ファイルの生成

- software/app フォルダーに移動し、 Nios® Vアプリケーション・ソースコードを作成します。

- Nios Vコマンドシェルを起動します。

- 以下のコマンドを実行して、アプリケーション CMakeLists.txt を生成します。

niosv-app --app-dir=software/app --bsp-dir=software/bsp \

--srcs=software/app/<Nios V application source code>アプリケーション・プロジェクトの構築

インテルFPGA向けの RiscFree* IDE、Eclipse Embedded CDT、またはコマンドライン・インターフェイス (CLI) を使用して、アプリケーション・プロジェクトのビルドを選択できます。

CLIを使用する場合は、次のコマンドを使用してアプリケーションをビルドできます。

cmake -G "Unix Makefiles" -DCMAKE_BUILD_TYPE=Debug -B \

software/app/debug -S software/appmake -C software/app/debugアプリケーション (.elf) ファイルは、software/app/debug フォルダーに作成されます。

HEXファイルの生成

フラッシュデバイスのプログラミングに適した .jic ファイルを作成できるように、アプリケーションの .elf ファイルから .hex ファイルを生成する必要があります。

- Nios Vコマンドシェルを起動します。

- コンフィグレーションQSPIフラッシュからの Nios® Vプロセッサー・アプリケーションexecute-in-place (XIP) の場合、次のコマンドラインを使用して、アプリケーションのELFをHEXに変換します。コマンドは、アプリケーション (.hex) ファイルを作成します。

elf2flash --input software/app/debug/<Nios V application>.elf \

--output flash.srec --reset <reset offset + base address of GSFI AVL MEM> \

--base <base address of GSFI AVL MEM> \

--end <end address of GSFI AVL MEM>riscv32-unknown-elf-objcopy --input-target srec --output-target ihex \

flash.srec <Nios V application>.hex