インテルのみ表示可能 — GUID: qiq1658192806238

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: qiq1658192806238

Ixiasoft

2.4.1. リセット要求インターフェイス

Nios® Vプロセッサーには、オプションのリセット要求機能が含まれています。リセット要求機能は、reset_req 信号と reset_req_ack 信号で構成されます。

プラットフォーム・デザイナーでリセット要求をイネーブルするには、

- Nios® V Processor IP Parameter Editorを起動します。

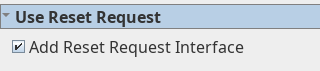

- Use Reset Request設定で、Add Reset Request Interfaceオプションをオンにします。

図 11. Nios® Vプロセッサーのリセット要求のイネーブル

reset_req 信号は、割り込みのように機能します。reset_req をアサートすると、コアへのリセットが要求されます。コアは未処理のバス・トランザクションがその動作を完了するのを待ちます。例えば、保留中のメモリー・アクセス・トランザクションがある場合、コアは完全な応答を待ちます。同様に、コアは保留中の命令応答を受け入れますが、reset_req 信号を受信した後は命令要求を発行しません。

リセット動作は、次のフローで構成されています。

- 保留中の動作をすべて完了する

- 内部パイプラインをフラッシュする

- Program Counter命令をリセットベクトルに設定する

- コアをリセットする

リセット動作全体には、数クロックサイクルかかります。reset_req_ack がアサートされてコアリセット動作が正常に完了したことを示すまで、reset_req はアサートされたままにする必要があります。そうしないと、コアの状態が非確定的になります。