インテルのみ表示可能 — GUID: izi1638888032251

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: izi1638888032251

Ixiasoft

4.5.1.3. GSFIブートローダー・デザイン例

IP CatalogからGSFI Bootloader Example Designを生成できます。デザイン例は、インテルArria 10 SoC開発キットに基づいています。提供されたスクリプトを使用して、ハードウェアとソフトウェアのデザインが生成され、それぞれSRAM Object Files (.sof) とJTAG Indirect Configuration Files (.jic) としてデバイスにプログラムされます。

プラットフォーム・デザイナーを使用してGSFIブートローダーのデザイン例を生成するには、次の手順を使用します。

- インテル® Quartus® Prime開発ソフトウェアで、Tools > Platform Designerに移動します。

- プラットフォーム・デザイナーで、IP Variantを選択します。

- Quartus projectでは、Noneを選択します。

- IP Variantダイアログボックスで、IPの任意の名前を指定します。

注: IPを保存する必要はありません。

- Component typeで、Selectをクリックします。

- IP Catalogが表示されます。

- Nios V/m Processor Intel FPGA IPを検索します。

- IPデザインを作成します。

図 44. Nios® V/m Processor Intel® FPGA IP向けのIPパラメーター・エディター

- Example Design: “GSFI Bootloader Example Design”をクリックし、プロジェクト・フォルダーを選択します。

- IP Parameter Editorを閉じます。Save changes?というプロンプトが表示されても、IPを保存する必要はありません。Don’t Saveをクリックします。

- プロジェクト・フォルダーにデザイン例を解凍します。デザイン例ファイルとその説明については、ブートーコピア (GSFIブートローダー) を使用してコンフィグレーションQSPIフラッシュからRAMにコピーされたNios Vプロセッサー・アプリケーションの図および、ファイルの説明 (GSFI Bootloader Example Design) の表を参照してください。

CLIを使用してGSFI Bootloader Example Designを生成するには、次のコマンドを使用します。

<Intel Quartus Prime installation directory>/niosv/bin/niosv-shellip-deploy --component-name=intel_niosv_m --output-name=niosv_m.ipqsys-generate niosv_m.ip --example_design=niosv_m.gsfi_bootloader_example_designunzip a10soc_niosv_m_gsfi_bootloader_example_design.zip| ファイル | 説明 |

|---|---|

| software/app | ソフトウェア・アプリケーションのソースコードを含むフォルダー。 |

| bsp_script.tcl | BSP EditorをコンフィグレーションするためのTCLスクリプト。 |

| create_design.py | デザイン例をビルドし、デバイスをプログラムするためのPythonスクリプト。 |

| flash_image.cof | Convert Programming Fileツールを使用して、JICファイルを生成するための情報を提供します。 |

| qsys_system_script.tcl | デザイン例の .qsys ファイルを生成するTCLスクリプト。 |

| readme.txt | デザイン例をビルドするための説明と手順。 |

| toggle_issp.tcl | In-System Sources and Probes (ISSP) を介してデザインをリセットするTCLスクリプト。 |

| top.sdc | デザイン例Synopsys* Design Constraints (.sdc) ファイル。 |

| top.tcl | デザイン例の .qpf ファイルと .qsf ファイルを生成するTCLスクリプト。 |

| top.v | トップレベルのVerilogデザイン。 |

GSFIブートローダー・デザイン例の実行

- Nios Vコマンドシェルを起動します。

- create_design.py を実行してデザイン例をビルドし、インテルArria 10 SoC開発キットをプログラムします。

quartus_py create_design.py

- Nios Vプロセッサーをリセットします。

quartus_stp -t toggle_issp.tcl

- JUARTターミナルを実行して、出力を表示します。

juart-terminal

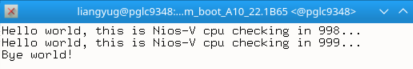

図 45. GSFIブートローダー・デザイン例

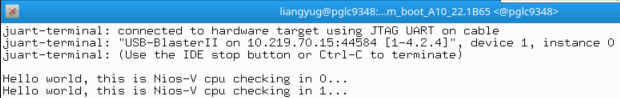

図 46. JUARTターミナル出力

- はじめに、次のメッセージがウィンドウに表示されます。

- 最後に到達すると、次のメッセージがウィンドウに表示されます。