インテルのみ表示可能 — GUID: hzy1630477484163

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: hzy1630477484163

Ixiasoft

1.4.2.1.2. プラットフォーム・デザイナーにおける Nios® V/mプロセッサーのデザイン例システムの生成

プラットフォーム・デザイナーで Nios® V/mプロセッサーのデザイン例システムを生成するには、次の手順を実行します。

- インテル® Quartus® Prime開発ソフトウェアで top.qpf プロジェクト・ファイルを開きます。Tool > Platform Designerに移動します。

- 新しいプラットフォーム・デザイナー・システムを作成し、sys.qsys という名前を付けます。

- システムを保存します。

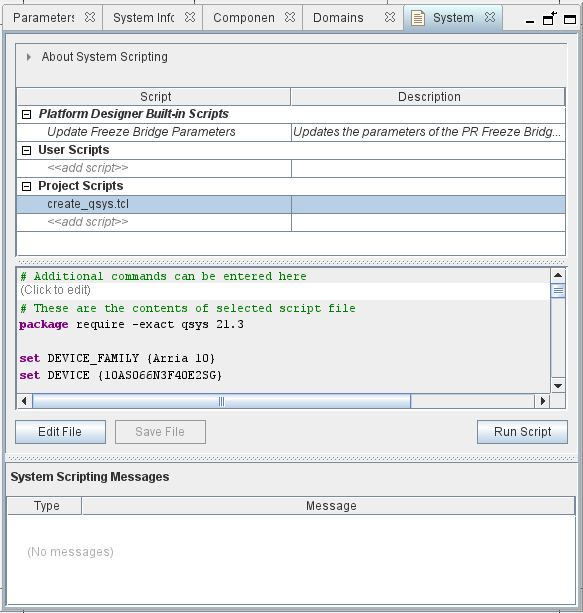

- プラットフォーム・デザイナーで、View > System Scriptingに移動します。System Scriptingウィンドウが表示されます。

- Project Scriptsで、Run Scriptを追加してクリックし、create_qsys.tcl スクリプトを実行します。

図 3. System Scriptingウィンドウ

- 生成されたプラットフォーム・デザイナー・システムは、クロックブリッジ、リセットブリッジ、 Nios® V/mプロセッサー、オンチップメモリー、およびJTAG UART IPで構成されます。

- Generate HDLをクリックして、システムHDLを生成します。

注: Arria 10 SoC開発キット以外の別のインテルFPGAデバイスをターゲットにするには、top.qsf ファイルでFAMILY、DEVICE、およびclock pinの割り当てを更新します。

- Processing > Start Compilationをクリックしてハードウェアのフルコンパイルを実行し、.sof ファイルを生成します。