インテルのみ表示可能 — GUID: dcy1638694505485

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: dcy1638694505485

Ixiasoft

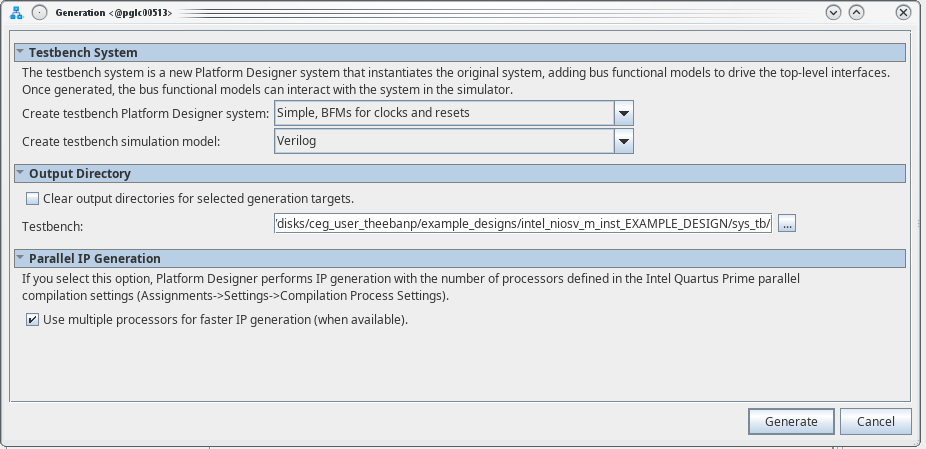

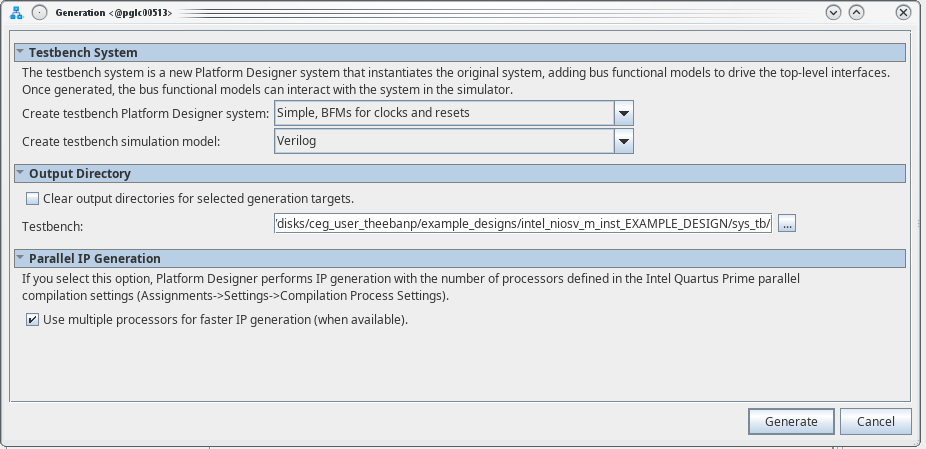

6.4.2. プラットフォーム・デザイナーでのシミュレーション環境のセットアップと生成

シミュレーション・ファイルを生成するには、次の手順を実行します。

- Intel Quartus Prime softwareを起動し、ToolsメニューからPlatform Designerを開きます。

- <your project design>.qsys ファイルを開きます。

注: シミュレーション・モデルを生成する前に、プラットフォーム・デザイナー・システムのビルドが完了していることを確認してください。

- Platform Designerで、Generate > Generate Testbench Systemに移動します。

- Generationウィンドウで、次のパラメーターをこれらの値に設定します。

- テストベンチのプラットフォーム・デザイナー・システムの作成 - Standard, BFMs for standard Platform Designer interfaces

システムにクロックとリセット以外のポートがエクスポートされている場合は、Standard, BFMs for standard Avalon interfacesを選択します。

- テストベンチのシミュレーション・モデルの作成 - Verilog

- Use multiple processors for faster IP generation (when available) を選択します。

- テストベンチのプラットフォーム・デザイナー・システムの作成 - Standard, BFMs for standard Platform Designer interfaces

- Generateをクリックし、プロンプトが表示されたらSaveをクリックします。

図 95. テストベンチの生成