インテルのみ表示可能 — GUID: kcl1638955238442

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: kcl1638955238442

Ixiasoft

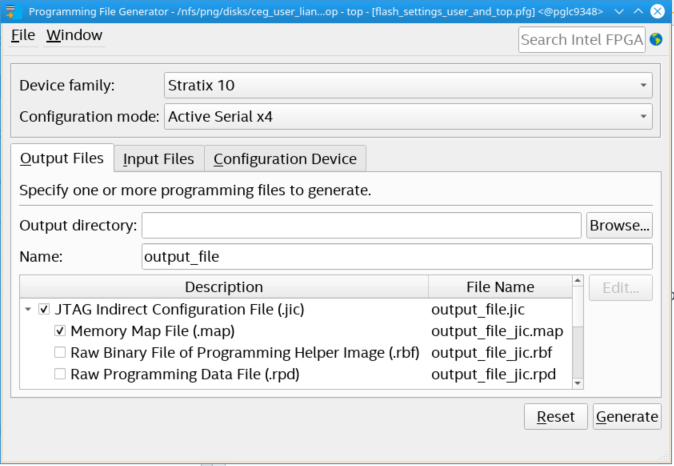

4.5.2.1.5. プログラミング・ファイルの生成

- File > Programming File Generatorに移動します。

- Configuration modeでは、Active Serial x4を選択します。

- Output Filesタブでは、JTAG Indirect Configuration File (.jic) を選択します。

図 65. Programming File Generator (Output Files)

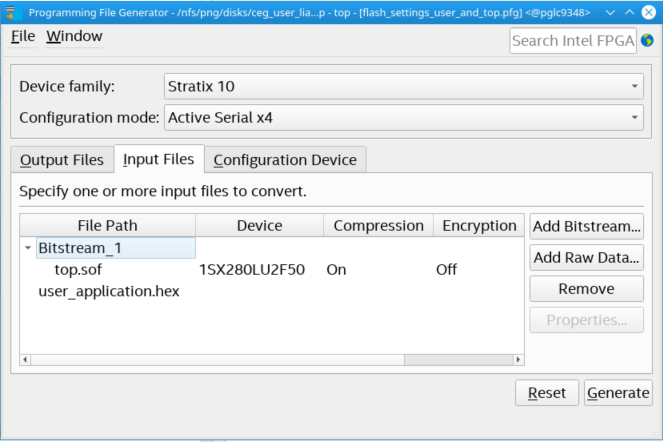

- Input Filesタブで、次の手順を実行します。

- Add Bitstreamをクリックして、SOFファイルを追加します。

- Add Raw Dataをクリックして、ユーザー・アプリケーション (.hex) ファイルを追加します。

- HEXファイルを選択して、Propertiesをクリックします。

- Bit Swap : Onを選択します。

図 66. Programming File Generator (Input Files)

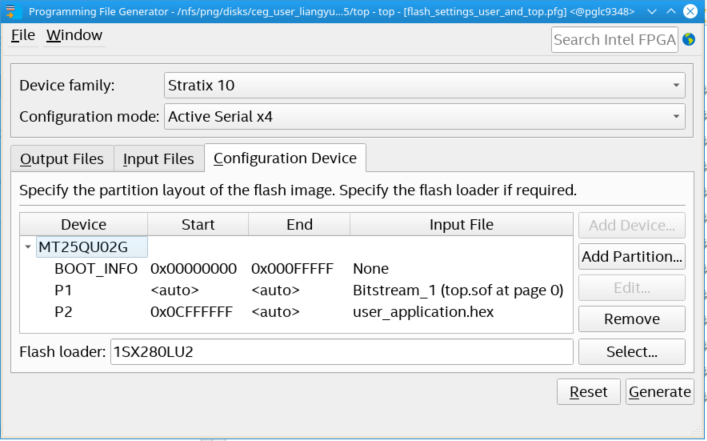

- Configuration Deviceタブで、

- Add Deviceをクリックして、フラッシュデバイスを追加します。

- サポートされているデバイスを使用している場合は、選択を行い、OKをクリックできます。それ以外の場合は、Apply the Configuration Device windowに進みます。

- フラッシュデバイスを選択してSOFファイルを追加し、Add Partitionをクリックします。

- フラッシュデバイスを選択してユーザー・アプリケーション (.hex) ファイルを追加し、Add Partitionをクリックします。Address ModeにStartを選択し、mailbox_bootcopier.c の PAYLOAD_OFFSET の値にStart addressを設定します。

- インテルFPGAデバイスに従って、Flash loaderを選択します。

図 67. Programming File Generator (Configuration Device)

- Add Deviceをクリックして、フラッシュデバイスを追加します。

- Generateをクリックして、JICファイルを生成します。

Configuration Deviceウィンドウの適用

Configuration Deviceを使用すると、特定のサポートされているデバイスまたはサポートされていないデバイスを選択できます。

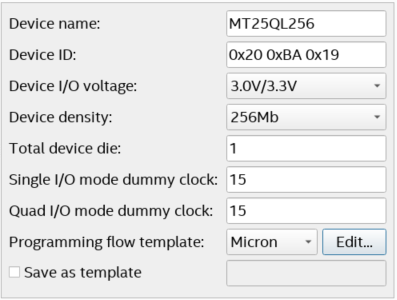

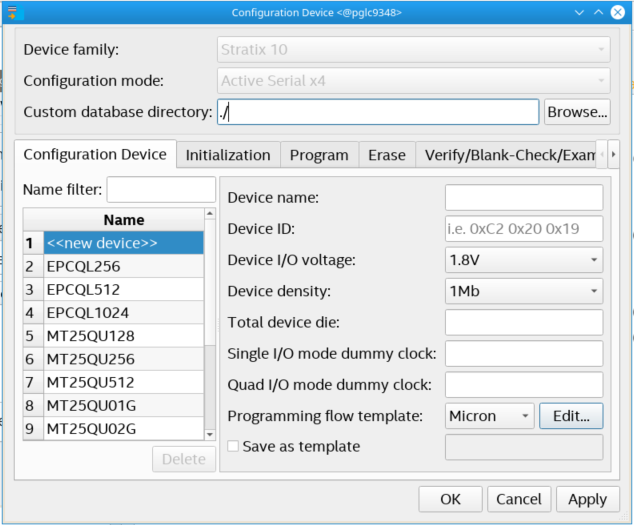

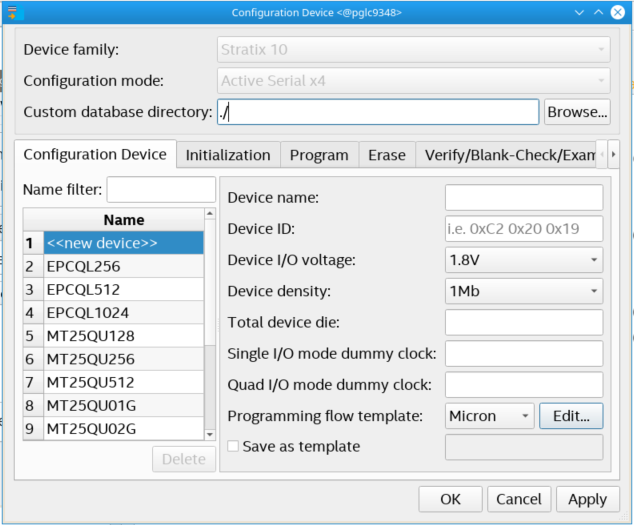

図 68. Configuration Deviceウィンドウ

- サポートされているデバイスを使用している場合は、選択してOKをクリックします。それ以外の場合は、次の手順に進みます。

- <<new device>>を選択します。

- Enter the information about Device name、Device ID、Device I/O voltage、Device density、Total device die、Dummy clock (Single I/OまたはQuad I/O mode)、およびProgramming flow templateに関する情報を入力します。

- Applyをクリックします。

注: Programming flow templateは、Initialization、Program、Erase、Verify/Blank-Check/Examine、およびTerminationにおけるフラッシュ動作のテンプレートを定義するのに役立ちます。デバイスを選択できない場合は、Generic Flash Programmer User Guide内、Modifying Programming Flowsを参照して、プログラミング・フローを変更してください。