インテルのみ表示可能 — GUID: zuk1638408180107

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: zuk1638408180107

Ixiasoft

1.4.4. FPGAデバイスへの Nios® V/mのプログラミング

Nios® V/mプロセッサー・ベースのシステムをFPGAにプログラムし、アプリケーションを実行するには、インテルQuartus Programmerツールを使用します。

- FPGAデバイス内に Nios® V/mプロセッサーを作成するには、次のコマンドを使用して .sof ファイルをボードにダウンロードします。

Windowsでは、

quartus_pgm -c 1 -m JTAG -o p;top.sof@1Linuxでは、quartus_pgm -c 1 -m JTAG -o p\;top.sof@1注:- -c 1 は、Host Computerに接続されているケーブル番号を示しています。

- @1 はJTAG Chainのデバイス・インデックスを参照しており、ボードによって異なる場合があります。

- Hello Worldアプリケーション・プログラムを実行するには、toggle_issp.tcl スクリプトを使用して Nios® V/mプロセッサー・システムをリセットします。

quartus_stp -t toggle_issp.tcl - niosv-download コマンドを使用して..elf をダウンロードします。

niosv-download <elf file>注: プラットフォーム・デザイナーでのコンフィグレーション中にEnable Debugオプションを設定して、niosv-download コマンドを使用します。 - JTAG UARTターミナルを使用して、 Nios® V/mプロセッサー・システムのstdoutおよびstderrを出力します。

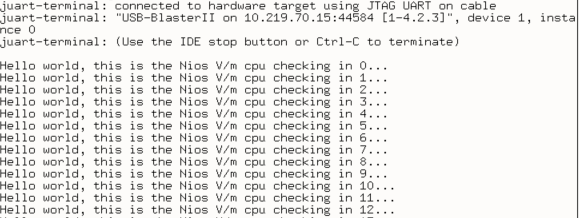

juart-terminal - 次の図に示すように、Hello Worldアプリケーションが表示されます。

図 6. hello.cを使用したHello Worldアプリケーションの出力

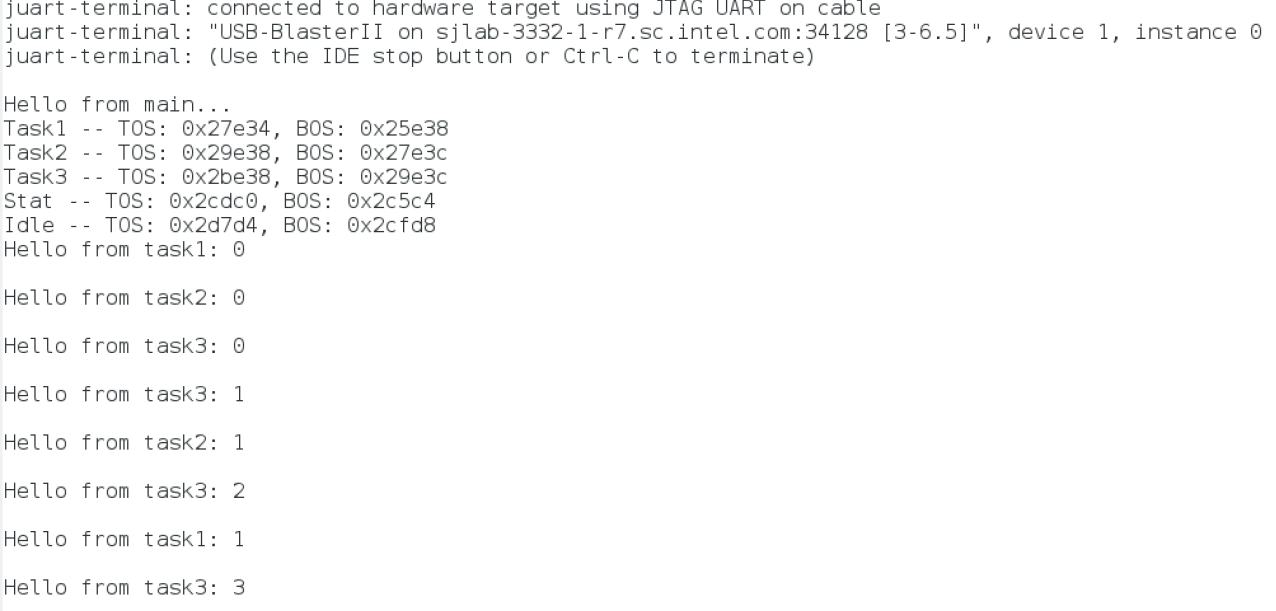

図 7. hello_ucosii.cを使用したHello Worldアプリケーションの出力

図 7. hello_ucosii.cを使用したHello Worldアプリケーションの出力