インテルのみ表示可能 — GUID: doh1638499137139

Ixiasoft

1. Nios® Vエンベデッド・プロセッサーについて

2. インテル® Quartus® Prime開発ソフトウェアおよびプラットフォーム・デザイナーを使用した Nios® Vプロセッサーのハードウェア・システム・デザイン

3. Nios® Vプロセッサー・ソフトウェアのシステムデザイン

4. Nios® Vプロセッサーのコンフィグレーションと起動ソリューション

5. Nios® Vプロセッサー - MicroC/TCP-IPスタックの使用

6. Nios® Vプロセッサーのデバッグ、検証、およびシミュレーション

7. Nios® Vプロセッサー - リモート・システム・アップデート

8. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックのアーカイブ

9. Nios® Vエンベデッド・プロセッサー・デザイン・ハンドブックの改訂履歴

インテルのみ表示可能 — GUID: doh1638499137139

Ixiasoft

4.6.1.1. ハードウェア・デザインフロー

以下の項では、OCRAMから Nios® Vプロセッサー・アプリケーション用のブート可能なシステムをビルドするための段階的な方法について説明します。以下の例は、インテルArria 10 SoC開発キットを使用してビルドされています。

IPコンポーネントの設定

- インテル® Quartus® Primeおよびプラットフォーム・デザイナーを使用して、 Nios® Vプロセッサー・プロジェクトを作成します。

- On-Chip Memory (RAM or ROM) Intel FPGAがプラットフォーム・デザイナー・システムに追加されていることを確認します。

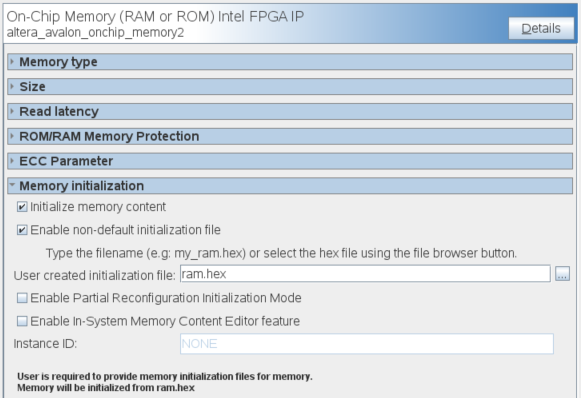

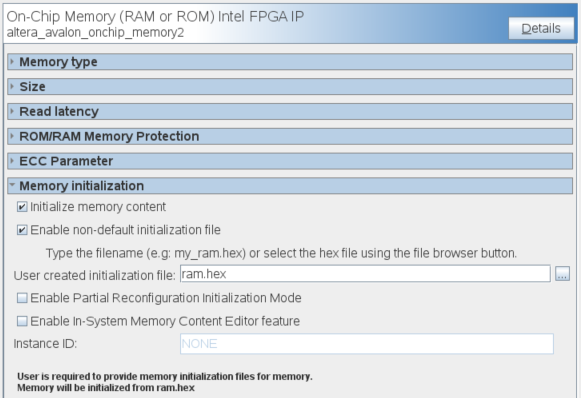

- オンチップメモリーの ram.hex でInitialize memory contentおよびEnable non-default initialization fileをイネーブルします。

図 74. Nios® Vプロセッサー・プロジェクトの接続

図 75. On-Chip Memory (RAM or ROM) Intel FPGA IPのパラメーター設定

Nios® Vプロセッサーのリセット・エージェントの設定

- Nios® Vプロセッサー・パラメーター・エディターで、Reset AgentをOCRAMに設定します。

図 76. Nios Vプロセッサー・パラメーター・エディターの設定

- Generate HDLをクリックすると、Generationダイアログボックスが表示されます。

- 出力ファイルの生成オプションを指定し、Generateをクリックします。

インテル® Quartus® Primeの設定

- インテルQuartus Prime開発ソフトウェアで、Assignment ➤ Device ➤ Device and Pin Options ➤ Configurationをクリックします。

- FPGAコンフィグレーション・スキームに従って、Configuration schemeを設定します。

- OKをクリックして、Device and Pin Optionsウィンドウを終了します。

- OKをクリックして、Deviceウィンドウを終了します。

- Start Compilationをクリックして、プロジェクトをコンパイルします。