インテルのみ表示可能 — GUID: qrj1636757811923

Ixiasoft

インテルのみ表示可能 — GUID: qrj1636757811923

Ixiasoft

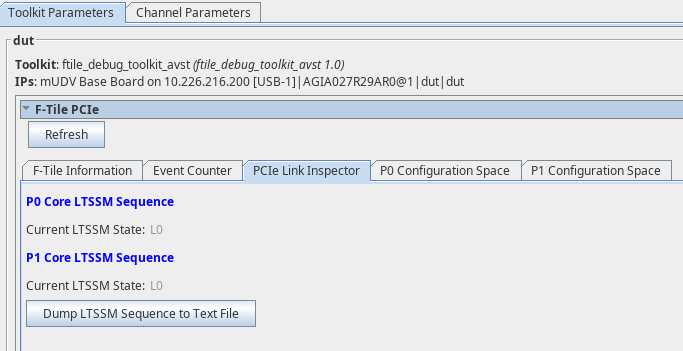

8.2.5. F-タイル・リンク・インスペクターの使用

リンク・インスペクターは、 PCIeリンク・インスペクター デバッグ・ツールキットを開いた後のタブ。

リンクインスペクターは、Enable Debug Toolkitが有効になっている場合、デフォルトで有効になっています。

Dump LTSSM Sequence to Text Fileボタンが最初にクリックされると、LTSSM情報を含むテキストファイル(ltssm_sequence_dump_p*.txt)が、システム・コンソール・ウィンドウが開いた場所に作成されます。PCIeトポロジに応じて、最大4つのテキストファイルが存在する可能性があります。後続のLTSSMシーケンスダンプは、それぞれのファイルに追加されます。

LTSSM State | Timer (ns) | LTSSM State # 0x11 L0 | 126639826 | 0 0xd RECOVERY_LOCK | 3708 | 1 0x5 PRE_DETECT_QUIET | 55730 | 2 0x0 DETECT_QUIET | 114539904 | 3 0x1 DETECT_ACTIVE | 560 | 4 0x6 DETECT_WAIT | 12582936 | 5 0x1 DETECT_ACTIVE | 552 | 6 0x0 DETECT_QUIET | 12582936 | 7 0x1 DETECT_ACTIVE | 560 | 8 0x6 DETECT_WAIT | 12582936 | 9 0x1 DETECT_ACTIVE | 560 | 10 0x2 POLLING_ACTIVE | 25855048 | 11 0x3 POLLING_COMPLIANCE | 64165384 | 12 0x5 PRE_DETECT_QUIET | 16850 | 13 0x0 DETECT_QUIET | 38471890 | 14 0x1 DETECT_ACTIVE | 560 | 15 0x6 DETECT_WAIT | 12582936 | 16 0x1 DETECT_ACTIVE | 552 | 17 0x2 POLLING_ACTIVE | 25860536 | 18 0x3 POLLING_COMPLIANCE | 13688808 | 19 0x2 POLLING_ACTIVE | 65696 | 20 0x4 POLLING_CONFIG | 50331672 | 21 0x5 PRE_DETECT_QUIET | 1048 | 22 0x0 DETECT_QUIET | 1568 | 23 0x1 DETECT_ACTIVE | 560 | 24 0x2 POLLING_ACTIVE | 351712 | 25 0x4 POLLING_CONFIG | 486576 | 26 0x7 CONFIG_LINKWD_START | 160 | 27 0x8 CONFIG_LINKWD_ACCEPT | 832 | 28 0x9 CONFIG_LANENUM_WAIT | 1808 | 29 0xa CONFIG_LANENUM_ACCEPT | 128 | 30 0xb CONFIG_COMPLETE | 1056 | 31 0xc CONFIG_IDLE | 1112 | 32 0x11 L0 | 16 | 33 0xd RECOVERY_LOCK | 520 | 34 0xf RECOVERY_RCVRCFG | 67200 | 35 0xe RECOVERY_SPEED | 566460 | 36 0xd RECOVERY_LOCK | 16 | 37 0x20 RECOVERY_EQ0 | 10485762 | 38 0x21 RECOVERY_EQ1 | 256 | 39 0x22 RECOVERY_EQ2 | 1712884 | 40 0x23 RECOVERY_EQ3 | 5188070 | 41 0xd RECOVERY_LOCK | 146 | 42 0xf RECOVERY_RCVRCFG | 438 | 43 0x10 RECOVERY_IDLE | 64 | 44 0x11 L0 | 186 | 45 0xd RECOVERY_LOCK | 788 | 46 0xf RECOVERY_RCVRCFG | 2294 | 47 0xe RECOVERY_SPEED | 575050 | 48 0xd RECOVERY_LOCK | 8 | 49 0x20 RECOVERY_EQ0 | 10485762 | 50 0x21 RECOVERY_EQ1 | 134 | 51 0x22 RECOVERY_EQ2 | 1481458 | 52 0x23 RECOVERY_EQ3 | 4492962 | 53 0xd RECOVERY_LOCK | 76 | 54 0xf RECOVERY_RCVRCFG | 228 | 55 0x10 RECOVERY_IDLE | 44 | 56 0x11 L0 | - | Current 現在のLTSSMの状態は: L0

各LTSSMモニターには、時間値とキャプチャされたLTSSM状態を格納するFIFOがあります。 LTSSM状態をダンプすることを選択した場合、読み取りはFIFO要素に依存し、FIFOを空にします。

リンクインスペクターは、状態遷移がある場合にのみFIFOに書き込みます。リンクがL0で安定している場合、書き込みは行われないため、テキストファイルはダンプされません。

LTSSMシーケンスをダンプする場合、それぞれのコアのFIFOステータスの単一の読み取りが実行されます。空のステータスとFIFOにあるエントリーの数に応じて、連続した読み取りが実行されます。