インテルのみ表示可能 — GUID: wvf1617310042704

Ixiasoft

インテルのみ表示可能 — GUID: wvf1617310042704

Ixiasoft

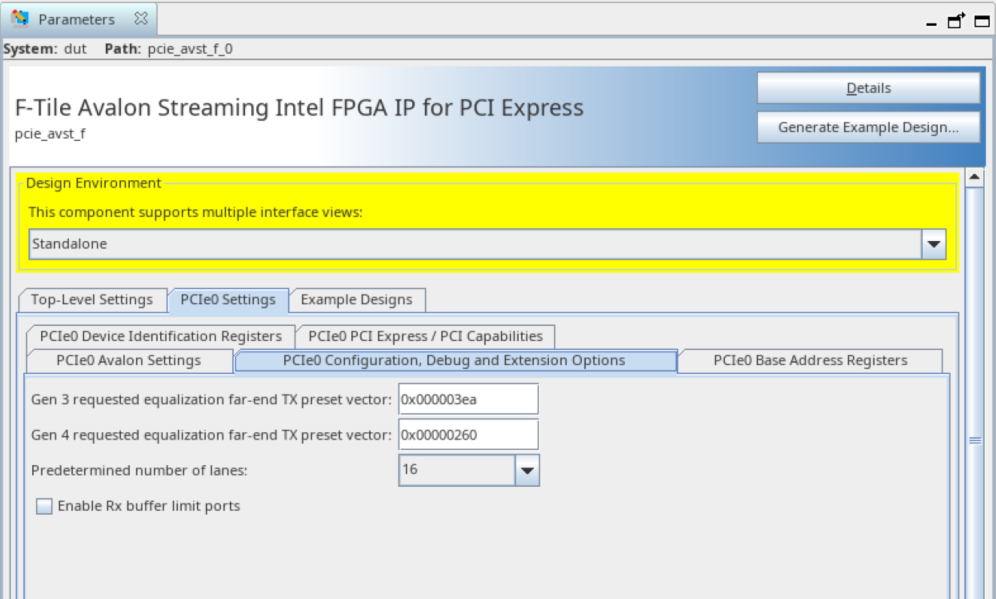

6.2.5. Configuration, Debug and Extension Options

| パラメーター | 値 | デフォルト値 | 説明 |

|---|---|---|---|

| Gen 3 Requested equalization far-end TX preset vector | 0~65535 | 0x00000020 (サフィックス VR0、VR1、または VR2 で終わる OPN を持つ F-タイルデバイスの場合) 0x0000030a (サフィックス VR3 または AA で終わる OPN を持つ F-タイルデバイスの場合) |

Gen 3 が要求したフェーズ 2/3 遠端 TX プリセット ベクトルを指定します。 |

| Gen 4 Requested equalization far-end TX preset vector | 0~65535 | 0x00000020 (サフィックス VR0、VR1、または VR2 で終わる OPN を持つF-タイルデバイスの場合) 0x00000060 (サフィックス VR3 または AA で終わる OPN を持つ F-タイルデバイスの場合) |

Gen4要求フェーズ2/3遠端TXプリセットベクトルを指定します。ほとんどのデザインでは、デフォルトとは異なる値を選択することはお勧めしません。

注: インテル® Quartus® Primeプロ・エディション バージョン 23.1 では、サフィックス VR3 または AA で終わる OPN を持つ F-タイルデバイスのこのパラメータのデフォルト値が誤って 0x00000060 に設定されます。 IP を生成する前に、この値を手動で 0x00000260 に設定する必要があります。

|

| Enable RX Buffer Limit Ports | True/False | False | 選択すると、RXバッファー制限ポートがエクスポートされ、RX投稿、非投稿、およびCplDパケットのバッファー制限を制御できます。それ以外の場合は、最大バッファーサイズが使用されます。 |

| 所定のレーン数 | 16 8 4 2 1 |

最大リンク幅 | 接続されている良好なレーンの数を定義します。 受信機を検出する「壊れた」または「未使用の」レーンを無視するために、有効なリンク幅を制限するために使用されます。 Polling.ActiveおよびL2.IdleでElectricalIdleからの終了を確認するレーンの数を示します。 LTSSMは、サブステートの検出中に、不良レーンまたは破損レーンのレシーバーを検出する可能性があります。ただし、そのようなレーンが電気アイドルを終了できず、有効なリンクがコンフィグレーションされない可能性もあります。この値は、PCI Expressベース仕様のセクション4.2.6.2.1では「所定のレーン数」と呼ばれています。 システムに未使用のレーンがある場合は、レーン数を反映するようにこのレジスターの値を変更する必要があります。たとえば、使用されているレーンの1つが不良であることがわかった場合は、「所定のレーン数」の値を減らす必要があります。 |

| Enable Prefetchable Memory 64-bit address support |

True/False |

True |

RP モードの場合、サポートされるプリフェッチ可能なメモリ範囲が 64 ビットであることを示します。 |