インテルのみ表示可能 — GUID: kux1613963837075

Ixiasoft

インテルのみ表示可能 — GUID: kux1613963837075

Ixiasoft

3.1.2. refclk

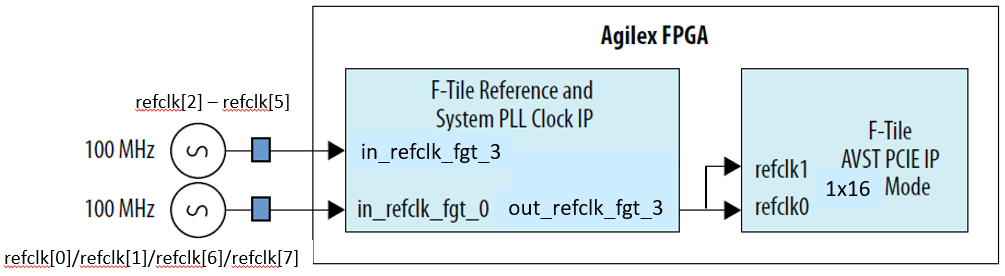

パッケージレベルでは、FGTPMA用の10個の基準クロックピンがあります。FGT リファレンス・クロック (refclk[0] ~ refclk[7]) のうち 8 つは、PCI Express チャネルのリファレンス・クロック入力として使用できます。 PCI Express 用の F-タイル Avalon ストリーミング IP には、IP のハード IP モード・コンフィグレーションに応じて、最大 4 つの基準クロック ポート (refclk0 ~ refclk3) があります。複数のFGTクワッドにまたがるハードIPモードの場合、クワッドがアクセスできる基準クロックピンを使用する必要があります。 HIPモードに応じて、 インテル® Quartus® Prime デザインでIPの基準クロックポートを対応する基準クロックピンに割り当てる必要があります。

F-タイル・リファレンスおよびシステム PLL クロックのインテル FPGA IP は、F-タイル Avalon ストリーミング PCI Express デザインに必要な IP です。 PCI Express チャネルの基準クロックをコンフィグレーションし、システム PLL もコンフィグレーションします。

次の表は、ハードIPモードに応じた、PCI Express用のF-タイル Avalon ストリーミング IPの基準クロックピンの基準クロックポートへのマッピングを示しています。

| モード | refclk0 port | refclk1 port | refclk2 port | refclk3 port |

|---|---|---|---|---|

| 1 x16 | refclk[2] or refclk[3] or refclk[4] or refclk[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] pin | なし | N/A |

| 1 x8 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 2 x8 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin | N/A | N/A |

| 1 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 2 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 4 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin |

- 1 x16、1 x8、および1 x4モードの場合、refclk0ポートとrefclk1ポートの両方を、「F-タイル Reference andSystemPLLClocks」IPからの単一のoutrefclk_fgt_i(i = 0〜7)ポートに接続する必要があります。

- 2 x8、2 x4、および4 x4モードの場合、ユーザーは、すべてのrefclkポートで単一のrefclkソースを共有し、「F-タイル Reference and SystemPLLClocks」 IPから単一のoutrefclk_fgt_i(i = 0〜7)ポートに接続するオプションがあります。

- 独立したrefclkソースは2x8および4x4モードでサポートされていますが、2x4、2 x8および4 x4モードではサポートされていません。

2x8モードでは、refclk0ポートとrefclk1ポートを、パッケージレベルで基準クロックピンに接続された単一の100 MHzクロックソース、またはシステム・アーキテクチャーに応じて2つの独立した100MHzソースのいずれかで駆動できます。たとえば、システムの各x8ポートが個別のCPU/ルートコンプレックスに接続されている場合、独立したクロックソースを使用して基準クロックピンを駆動する必要がある場合があります。PERST# クロックソースの安定性を示す必要があります。

4X4モードでは、 refclk0に refclk3 システム・アーキテクチャーに応じて、単一の100 MHzクロックソースを備えたポートは、パッケージレベルで基準クロックピンに接続するか、2つの独立した100MHzクロックソースまたは4つの独立したクロックソースに接続します。PERST# クロックソースの安定性を示す必要があります。

- PCIe リンクのトレーニングのタイミング仕様への準拠が必要な場合は、デバイス・コンフィギュレーションを開始する前に、システム PLL への基準クロックが利用可能で安定している必要があります。システム PLL IP のRefclk is available at power-onパラメーターをOnに設定する必要があります。独立したフリーランニング・クロック・ソースからリファレンス・クロックを取得します。あるいは、デバイス・コンフィギュレーションの開始前に PCIe リンクからの基準クロックが利用可能であることが保証されている場合は、それを使用してシステム PLL を駆動できます。PCIe リンクrefclkが一度有効になると、ダウンすることはできません。

- PCIe リンクのトレーニングのタイミング仕様への準拠が必要なく、デバイス・コンフィギュレーションが開始される前にシステム PLL への基準クロックが利用できない可能性がある場合は、システム PLL IP のRefclk is available at power-onパラメーターをOffに設定する必要があります。この場合、PCIe リンクからの基準クロックを使用してシステム PLL を駆動できます。システム PLL は、リファレンス・クロックが使用可能であることを通知するグローバル Avalon メモリー・マップ・インターフェース書き込み操作を実行するまで、リファレンス・クロックにロックしません。

以下の図は、独立した基準クロックがシステム PLL(in_refclk_fgt_0 ポート経由)を駆動する例を示しています。 PCIe リンクからの基準クロックは共有されません。これは、デバイスのコンフィギュレーションが開始される前には利用できません。

システム PLL の基準クロックが立ち上がると、デバイスの動作全体を通じて安定して存在し、低下してはなりません。この要件を遵守できない場合は、デバイスをリコンフィグレーションする必要があります。