インテルのみ表示可能 — GUID: rwp1637023783395

Ixiasoft

インテルのみ表示可能 — GUID: rwp1637023783395

Ixiasoft

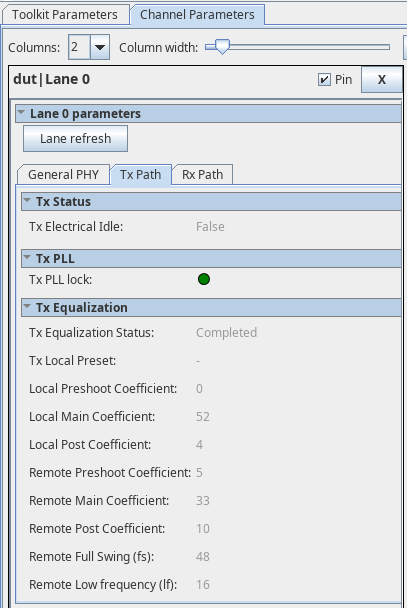

8.2.4.3.2. TXパス

このタブでは、選択したチャンネルの送信機設定を監視できます。

| パラメーター | 値 | 説明 | |

|---|---|---|---|

| TX Status | TX電気的アイドル | True, False | TXが電気的にアイドル状態にあるかどうかを示します。 True:TXが電気的にアイドル状態であることを示します。 False:TXが電気的アイドル状態にないことを示します。 |

| TX PLL | TX PLLロック | 緑、赤 | CMU PLLがロックされていることを示します。 CMU PLLがロックされていることを示します。 赤:TXPLLはロックされていません。 |

| TXイコライゼーション | TXイコライゼーション・ステータス | 試行されなかった、完了した、失敗した | 送信機のイコライゼーションステータスを示します。 TXローカルおよびリモートパラメーターは、イコライゼーションステータスの値が完了として返され、イコライゼーションが正常に完了したことを示す場合にのみ有効です。 |

| TXローカルプリセット | P0 to P10 | リンクトレーニングのイコライゼーションフェーズ中にリンクパートナーから要求されたF-タイル送信機ドライバーのプリセット値を示します。プリセットがこれらの値のいずれでもない場合、値は表示されません。 | |

| ローカルプレシュート係数 | リンクパートナーから要求された係数によって異なります。 |

F-タイル送信機ドライバー出力プリエンファシス(プリカーサー係数値)を示します。 |

|

| ローカル主係数 | リンクパートナーから要求された係数によって異なります。 |

F-タイル送信機ドライバー出力プリエンファシス(メインカーソル係数値)を示します。 |

|

| ローカルポスト係数 | リンクパートナーから要求された係数によって異なります。 |

F-タイル送信機ドライバーの出力プリエンファシス(カーソル後の係数値)を示します。 |

|

| リモートプレシュート係数(†) | リンクパートナーのトランスミッタドライバ出力に依存します。 | リンクトレーニングのイコライゼーションフェーズ中にF-タイルが受信した、リンクパートナーの送信機ドライバーの出力カーソル係数値を示します。 F-タイルがエンドポイントモードでコンフィグレーションされている場合、この値は、イコライゼーションのフェーズ2で受信した係数に対応します。 |

|

| リモートメイン係数(†) | リンクパートナーのトランスミッタドライバ出力に依存します。 | リンクトレーニングのイコライゼーションフェーズ中にF-タイルが受信した、リンクパートナーの送信機ドライバーの出力メインカーソル係数値を示します。 F-タイルがエンドポイントモードでコンフィグレーションされている場合、この値は、イコライゼーションのフェーズ2で受信した係数に対応します。 |

|

| リモートポスト係数(†) | リンクパートナーのトランスミッタドライバ出力に依存します。 | リンクトレーニングのイコライゼーションフェーズ中にF-タイルが受信した、リンクパートナーの送信機ドライバーの出力カーソル後係数値を示します。 F-タイルがエンドポイントモードでコンフィグレーションされている場合、この値は、イコライゼーションのフェーズ2で受信した係数に対応します。 | |

| リモートフルスイング(fs)(†) | リンクパートナーのデバイス機能によって異なります。 | リンクトレーニングのイコライゼーション・フェーズ中にリンクパートナーが使用するフルスイング値を示します。 | |

| リモート低周波(lf)(†) | リンクパートナーのデバイス機能によって異なります。 | リンクトレーニングのイコライゼーション・フェーズ中にリンクパートナーが使用する低頻度の値を示します。 |