インテルのみ表示可能 — GUID: zbq1636757711230

Ixiasoft

1. 頭字語

2. はじめに

3. IPアーキテクチャーと機能の説明

4. 高度な機能

5. インターフェイス

6. パラメーター

7. テストベンチ

8. トラブルシューティング/デバッグ

9. F-タイル Avalon ストリーミング・インテル FPGA IP for PCI Expressユーザーガイドのアーカイブ

10. F-タイル Avalon ストリーミング・インテル FPGA IP for PCI Express ユーザーガイドの改訂履歴

A. コンフィグレーション・スペース・レジスター

B. エンドポイントモードでのアドレス変換サービス(ATS)の実装

C. TLPバイパスモードでユーザー・アプリケーションに転送されるパケット

D. Root Port BFM

E. 独立したリセットに対する分岐エンドポイントのサポート

5.1. このボードについて

5.2. クロックおよびリセット

5.3. シリアル・データ・インタフェース

5.4. Avalon-ST インターフェイス

5.5. 割り込みインターフェイス

5.6. ハードIP Statusインターフェイス

5.7. エラー・インターフェイス

5.8. 10ビットタグサポートインターフェイス

5.9. コンプリーション・タイムアウト・エラー。

5.10. Power Management Interface

5.11. ホット・プラグ・インターフェイス(RPのみ)

5.12. ペイロード出力インターフェイス

5.13. コンフィグレーションインターセプトインターフェイス(EPのみ)

5.14. ハードIPリコンフィグレーション・インターフェイス

5.15. PHYリコンフィグレーション・インターフェイス

5.16. ページリクエストサービス(PRS)インターフェイス(EPのみ)

5.17. FLRインターフェイス信号

5.18. PTMインターフェイス信号

5.19. VFエラー・フラグ・インターフェイス信号

5.20. VirtIOPCIコンフィグレーション・アクセスインターフェイス信号

6.2.3.1. デバイス・ケイパビリティー

6.2.3.2. Link Capabilities

6.2.3.3. Legacy Interrupt Pin Register

6.2.3.4. MSI-X Capabilities

6.2.3.5. MSI-X Capabilities

6.2.3.6. スロット・ケイパビリティー

6.2.3.7. レイテンシー・トレランス・レポート(LTR)

6.2.3.8. Process Address Space ID (PASID)

6.2.3.9. Device Serial Number Capability

6.2.3.10. Page Request Service (PRS)

6.2.3.11. Access Control Service (ACS) Capabilities

6.2.3.12. 消費電力マネジメント

6.2.3.13. Vendor Specific Extended Capability (VSEC)

6.2.3.14. Precision Time Measurement (PTM)

6.2.3.15. Address Translation Services (ATS)

6.2.3.16. TLP Processing Hints (TPH)

6.2.3.17. VirtIOパラメーター

7.6.1. ebfm_barwrプロシージャー

7.6.2. ebfm_barwr_immプロシージャー

7.6.3. ebfm_barrd_waitプロシージャー

7.6.4. ebfm_barrd_nowtプロシージャー

7.6.5. ebfm_cfgwr_imm_waitプロシージャー

7.6.6. ebfm_cfgwr_imm_nowtプロシージャー

7.6.7. ebfm_cfgrd_waitプロシージャー

7.6.8. ebfm_cfgrd_nowtプロシージャー

7.6.9. BFMコンフィグレーション・プロシージャー

7.6.10. BFM共有メモリー・アクセス・プロシージャー

7.6.11. BFMログおよびメッセージ・プロシージャー

7.6.12. Verilog HDL Formattingファンクション

A.3.1. Intel定義のVSEC機能ヘッダー(オフセット00h)

A.3.2. インテル定義のベンダー固有のヘッダー(オフセット04h)

A.3.3. インテルマーカー(オフセット08h)

A.3.4. JTAGシリコンID(オフセット0x0C-0x18)

A.3.5. ユーザー設定可能なデバイスとボードID(オフセット0x1C-0x1D)

A.3.6. General Purpose Control and Status Register - 0xBB0

A.3.7. Uncorrectable Internal Error Status (修正不可能な内部エラーステータス) レジスター - 0xBB4

A.3.8. Uncorrectable Internal Error Mask (修正不可能な内部エラーマスク) レジスター - 0xBB8

A.3.9. Correctable Internal Error Status (修正可能な内部エラーマスク) レジスター - 0xBBC

A.3.10. Correctable Internal Error Mask (修正可能な内部エラーマスク) レジスター

インテルのみ表示可能 — GUID: zbq1636757711230

Ixiasoft

8.2.3. F タイル デバッグ ツールキットの起動

クイック・スタート・ガイドに従ってコンパイルしたデザインサンプルを使用して、F タイルのデバッグ・ツールキットに慣れてください。 「デザインサンプルの生成」および「デザイン サンプルのコンパイル」の手順に従って、このデザイン サンプルの SRAM オブジェクト ファイル (.sof) を生成します。

F タイルのデバッグ・ツールキットを使用するには、.sof をインテル開発キットにダウンロードします。 次に、システムコンソールを開き、デザインをシステムコンソールにもロードします。 .sof をシステムコンソールにロードすると、システムコンソールが NPDME を使用してデザインと通信できるようになります。NPDME は、JTAG ベースのAvalon-MMマスターです。PCIe デザインでAvalon-MMスレーブ・インターフェイスを駆動します。 NPDME を使用する場合、 インテル® Quartus® Primeソフトウェアはデバッグ・インターコネクト・ファブリックを挿入して JTAG に接続します。

これらのタスクを完了する手順は次のとおりです。

- インテル® Quartus® Primeプログラマーを使用して、.sof をインテル FPGA 開発キットにダウンロードします。

注: 正しく動作することを保証するには、 インテル® Quartus® Primeプロ・エディションのソフトウェアのフルインストールと、.sof の生成に使用したプログラマーおよび インテル® Quartus® Primeプロ・エディションのソフトウェアの インテル® Quartus® Primeと同じバージョンのデバイスを使用します。注: インテル® Quartus® Primeプロ・エディションのプログラマーとツールのスタンドアロン・インストールは機能しません。

- デザインをシステムコンソールにロードするには、次の手順を実行します。

- インテル® Quartus® Primeプロ・エディションのソフトウェアを起動します。

- Tools、System Debugging Tools、System Consoleの順に選択してSystem Consoleを起動します。

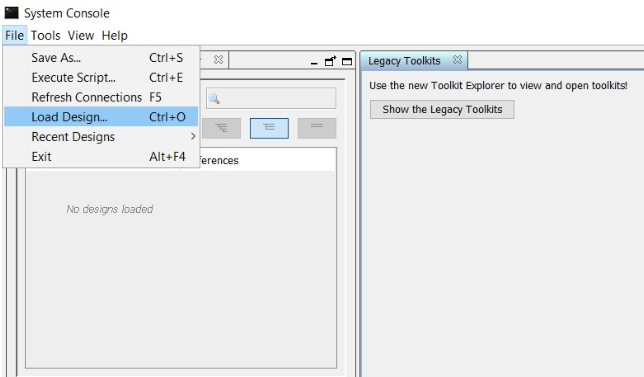

- System Console Fileメニューで、Load designを選択し、.sof ファイルを参照します。

- .sof を選択し、OKをクリックします。 .sof がシステムコンソールにロードされます。

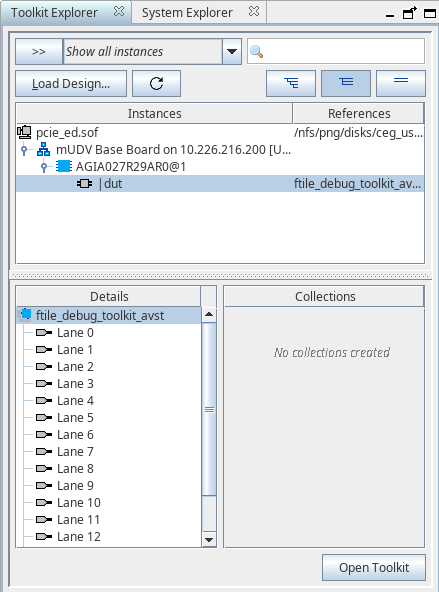

- System Console Toolkit Explorer ウィンドウには、F タイル デバッグ ツールキットが有効になっているデザイン内のすべての DUT がリストされます。

- 表示したい F タイルのデバッグ・ツールキットを含む DUT を選択します。 これにより、Detailsウィンドウでその DUT の Debug Toolkit インスタンスが開きます。

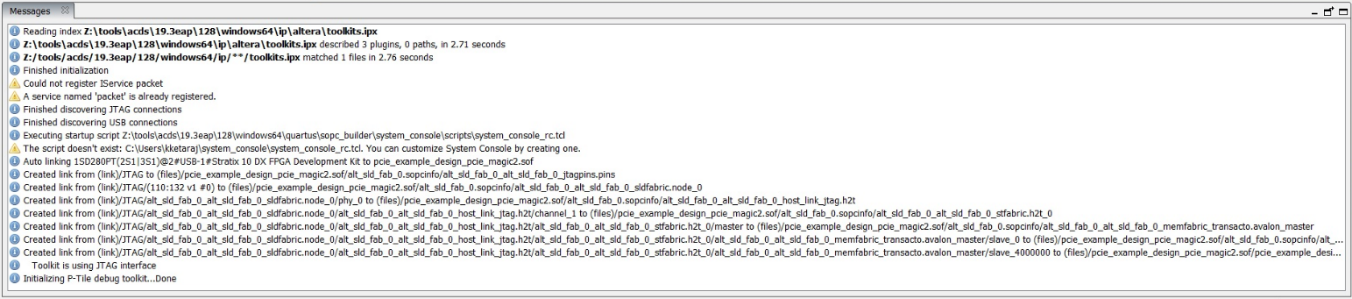

- ftile_debug_toolkit_avstをクリックして、ツールキットのインスタンスを開きます。 デバッグ ツールキットが初期化されロードされると、Messagesウィンドウに“Initializing F-Tile debug toolkit – done”というメッセージが表示されます。

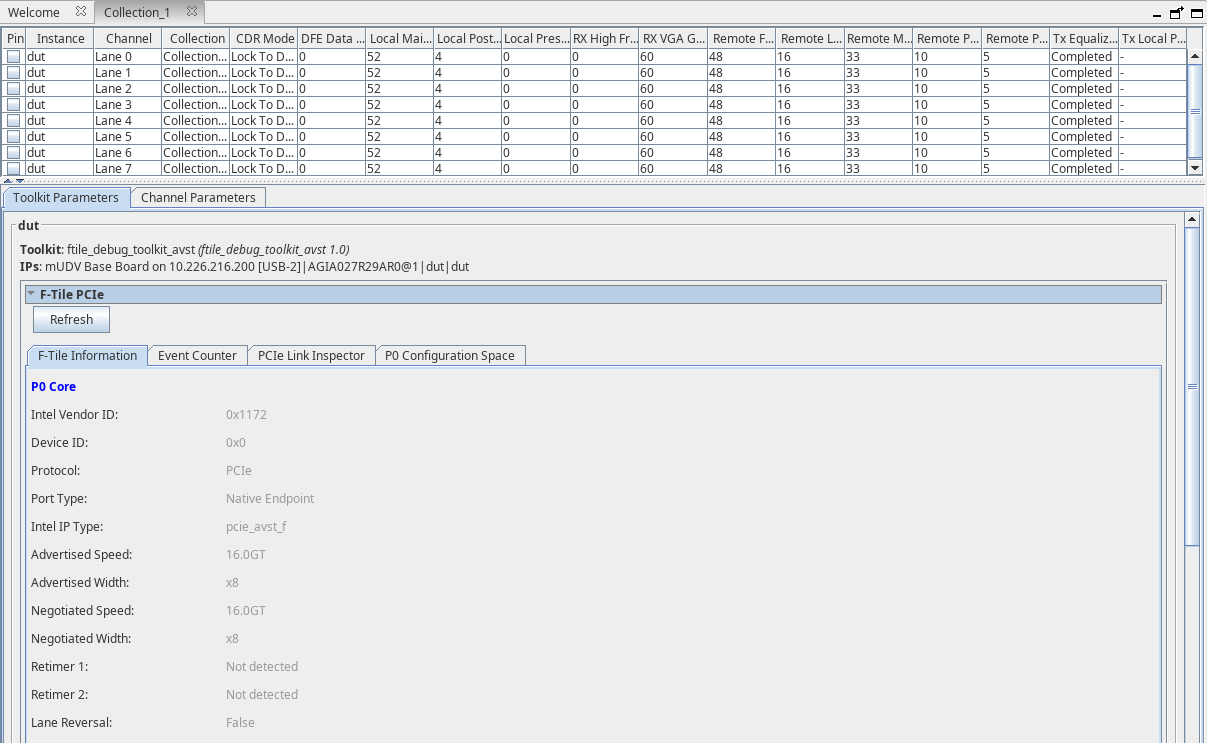

- 新しいウィンドウのMain viewが開き、そのインスタンス内のすべてのチャンネルが表示されます。

- 表示したい F タイルのデバッグ・ツールキットを含む DUT を選択します。 これにより、Detailsウィンドウでその DUT の Debug Toolkit インスタンスが開きます。