インテルのみ表示可能 — GUID: cjm1491782850405

Ixiasoft

インテルのみ表示可能 — GUID: cjm1491782850405

Ixiasoft

1.2.1. デザインブロックの再利用例

コア・パーティションの再利用例

典型的なコア・パーティションの再利用例では、デベロッパーはすでにデザイン要件を満たしているコア・パーティションをエクスポートします。デベロッパーはブロックを最適化してエクスポートするので、コンシューマーは、コンシューマー・プロジェクトで最適化を再度行うことなくブロックを再利用することができます。

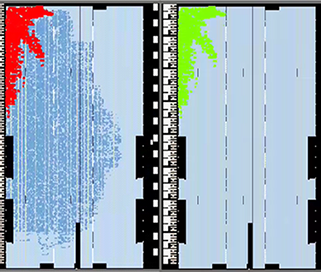

保存したい独自の特性を持つコアブロックをエクスポートして、他のプロジェクトでその機能または物理実装をレプリケーションできます。次の図では、デベロッパーはフロアプランの赤色のパーティションを再利用します。右側の別のプロジェクトのフロアプランでは緑色で表示されています。

ルート・パーティションの再利用例

典型的なルート・パーティションの再利用例では、デベロッパーは、他のプロジェクトでの再利用に適したペリフェラル・リソースとコアリソースを含むルート・パーティションを定義します。その一例が複数のデベロッパーやプロジェクトが使用できる開発キットです。

ルート・パーティションの再利用においては、各プロジェクトが同じ Intel® FPGAの部品番号、同じインターフェイスを持ち、同じ インテル® Quartus® Prime プロ・エディション開発ソフトウェア・バージョンを使用する必要があります。 次の例では、さまざまなペリフェラル・インターフェイスを含む最適化されたルート・パーティションの再利用について示しています。カスタムロジックを含むペリフェラル・リージョンの再利用コア・パーティションのみがコンシューマー・プロジェクト間で変更されます。

ルート・パーティションは複数のボードで再利用することができます。ルート・パーティションのデベロッパーは、必要なリソースすべてを使用し、期待されるデザイン要件を満たすデザインを作成すると同時に、コンシューマー開発のためのリージョン(ペリフェラル再利用コア)を確保します。その後デベロッパーはルート・パーティションを.qdbファイルでエクスポートし、 .qdbをそのパーティションのコンシューマーに渡します。

コンシューマーはルート・パーティションを再利用し、ペリフェラル再利用コア用に独自のRTLを追加します。このフローは、共通のルート・パーティションを持つ複数の異なるボード上での開発を可能にします。ルート・パーティションを再利用すると、デベロッパーがルート・パーティションをあらかじめ最適化しているため、コンシューマーの開発時間を節約できます。