インテルのみ表示可能 — GUID: bhc1411109478369

Ixiasoft

1.1. 概要

1.2. システムレベルのデバッグ・インフラストラクチャー

1.3. 仮想JTAG インターフェイスの概要

1.4. ランタイム通信

1.5. 仮想JTAG IP コアのインスタンス化

1.6. シミュレーション・サポート

1.7. デザインのコンパイル

1.8. SLD_NODE 検出と列挙

1.9. 仮想IR 命令レジスターのキャプチャ-

1.10. AHDL 関数プロトタイプ

1.11. VHDL コンポーネント宣言

1.12. VHDL LIBRARY-USE 宣言

1.13. TAP コントローラー・ステートマシン・デザイン例

1.14. ランタイムにおけるDCFIFO 内容の変更デザイン例

1.15. ハードワイヤード・リビジョン情報のオフロードデザイン例

1.16. 改訂履歴

インテルのみ表示可能 — GUID: bhc1411109478369

Ixiasoft

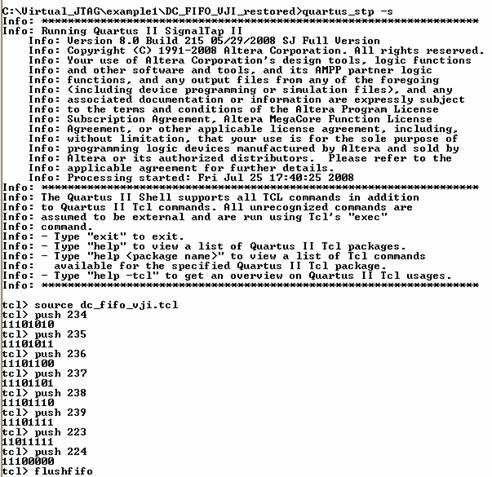

1.14.3. ランタイム通信

Tcl スクリプトのdc_fifo_vji.tcl には、それぞれ仮想JTAG 命令の1 つに対応する3 つのプロシージャーが含まれています。 以下の表では、各プロシージャーについて説明します。

| プロシージャー |

概要 |

|---|---|

| push [value] |

IR はPUSH 命令をシフトし、その後にValue 引数のDR シフトを実行します。 Value は256 未満の整数でなければなりません。 |

| pop |

IR はPOP 命令をシフトし、その後に8 ビットのDR シフトを実行します。 |

| flushfifo |

IR はFLUSH 命令をシフトします。 |

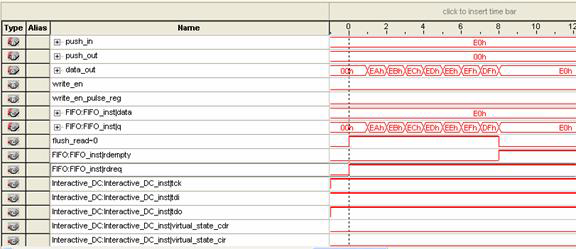

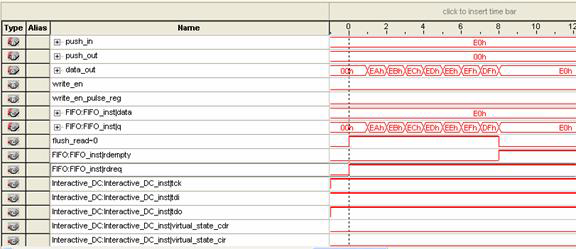

以下の図は、DCFIFO およびflushfifo コマンドにプッシュされた8 つの値のランタイム実行と、フラッシュ操作でのSignalTap II Logic Analyzer のトリガーキャプチャーを示しています。

図 23. ランタイム実行

図 24. フラッシュ操作におけるSignalTap II Logic Analyzer のトリガーキャプチャー