インテルのみ表示可能 — GUID: hqw1647318068947

Ixiasoft

インテルのみ表示可能 — GUID: hqw1647318068947

Ixiasoft

7.1.3.5. ダイナミック・リコンフィグレーション

Fタイルデバイスでダイナミック・リコンフィグレーションを実装するには、 Intel® FPGA IPカタログのF-Tile Dynamic Reconfiguration Suite IPを使用する必要があります。IPの詳細については、F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP ユーザーガイドを参照してください。

このIPを使用するには、F-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IPと、サポートする各データレートのセカンダリー・プロファイルを作成します。例えば、270Mbps (SD-SDI)、1.485Gbps (HDSDI)、および2.97Gbps (3G-SDI) の3つの異なるデータレートをサポートするトリプルレートSDIには、3つの異なるデータレート・コンフィグレーションを持つ1つのPHYベース・プロファイルと2つのセカンダリー・プロファイルが必要です。ただし、3G-SDIとSD-SDIはSDI II Intel® FPGA IPのトランシーバー処理で同じPHYコンフィグレーションを共有できるため、RX側のF-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IPで作成する必要があるセカンダリー・プロファイルは1つのみです。TX側では、IPがオーバーサンプリングを実行しており、データレート間のリコンフィグレーションが必要ないため、F-Tile PMA/FEC Direct PHY Intel® FPGA IPインスタンスのシングルレート・バージョンが使用されます。詳細については、TX Sampleのトピックを参照してください。ただし、デザインでNTSCおよびPALレートの2つのリファレンス・クロックの切り替えが必要な場合は、TX PLLリファレンス・クロックを別のクロックポートに接続するために、F-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IPが必要です。

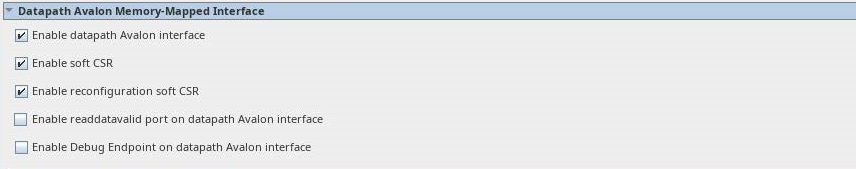

- Enable datapath Avalon interface

- Enable soft CSR

- Enable reconfiguration soft CSR

プロファイル・インスタンスとして機能するこれらのインスタンスをインスタンス化した後、reconfig_pdpクロック (F-Tile Dynamic Reconfiguration Suite Intel® FPGA IPの i_csr_clk ポートと同じクロックを共有することが可能) を接続して、ポートをリセットし、 Avalon®メモリーマップド・インターフェイス・ポートを終了する必要があります。リコンフィグレーション・グループを定義するには、プロジェクトの .qsf ファイルに次の割り当てを含める必要があります。

set_instance_assignment -name IP_RECONFIG_GROUP <your base profile ID> -to <Multirate PHY base profile instance> set_instance_assignment -name IP_COLOCATE F_TILE -from <Dynamic reconfig IP instance> -to <Multirate PHY base profile instance>

SDI II Intel® FPGA IPのデザイン例には、リコンフィグレーション・コントローラーのRTLモジュールと、SDI II IPとDynamic Reconfiguration Suite IPの間で相互作用するためのアービターが含まれています。RTL例の詳細については、F-Tile SDI II Intel® FPGA IP Design Example User Guideを参照してください。