インテルのみ表示可能 — GUID: xop1633471022804

Ixiasoft

インテルのみ表示可能 — GUID: xop1633471022804

Ixiasoft

10.1.4.2. ツールキット・パラメーター

Toolkit パラメーターの ウィンドウには、次のサブタブがあります。

Pタイルの情報

これは、初期化時に P-タイルのデバッグ・ツールキットによって読み出されたIP が生成されたときの PCIe IP Parameter Editor の PタイルPCIe IP パラメーター設定の概要をリストします。デザインでポート分岐が有効になっている場合 (x8x8 など)、このタブは各コア (P0 コア、P1 コアなど) の P タイル情報を取り込みます。

すべての情報は読み出し専用です。

Refresh ボタンをクリックして設定を読み込みます。

| パラメーター | 値 | 説明 |

|---|---|---|

| Intel Vendor ID | 1172 | IP パラメーター・エディタで設定されたベンダー ID を示します。 |

| Device ID | 0 | これは、ベンダーによって割り当てられたデバイスの一意の識別子です。 |

| Protocol | PCIe | プロトコルを示します。 |

| Port Type | Root Port, Endpoint 1 | ハード IP ポートのタイプを示します。 |

| Intel IP Type | intel_pcie_mcdma | 使用される IP タイプを示します。 |

| Advertised speed | Gen3、Gen4 | IP パラメーター・エディタでコンフィグレーションされたアドバタイズされた速度を示します。 |

| Advertised width | x16、x8 | IP パラメーター・エディタでコンフィグレーションされたアドバタイズ幅を示します。 |

| Negotiated speed | Gen3、Gen4 | リンク・トレーニング中にネゴシエートされた速度を示します。 |

| Negotiated width | x16、x8 | リンク・トレーニング中にネゴシエートされたリンク幅を示します。 |

| Link status | Link up, link down | リンク (DL) がアップしているかどうかを示します。 |

| LTSSM State | F タイル Avalon Streaming Intel FPGA IP for PCI Expressユーザーガイドを参照してください。 | リンクの現在の状態を示します。 |

| Lane Reversal | True/False | リンクで車線反転が発生するかどうかを示します。 |

| Retimer 1 | Detected, not detected | ルート ポートとエンドポイントの間でリタイマーが検出されたかどうかを示します。 |

| Retimer 2 | Detected, not detected | ルート ポートとエンドポイントの間でリタイマーが検出されたかどうかを示します。 |

| Tx TLP Sequence Number | Hexadecimal value | 送信 TLP の次の送信シーケンス番号を示します。 |

| Tx Ack Sequence Timeout | Hexadecimal value | ACK/NAK DLLP の受信によって更新される ACK シーケンス番号を示します。 |

| Replay Timer Timeout | Green, Red | Green: タイムアウトなし Red: タイムアウト |

| Malformed TLP Status | Green, Red | Green: 不正な形式の TLPがなし Red: 不正な形式の TLPが検出された |

| First Malformed TLP Error Pointer |

|

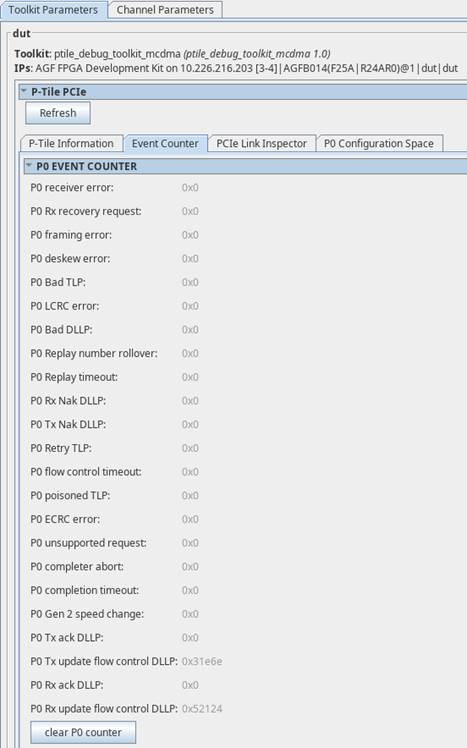

イベント・カウンタ

このタブでは、各ポートの受信エラー、フレーミング・エラーなどのエラー イベントを読み出すことができます。Clear P0 counter/Clear P1 counterをクリックしてエラーカウンターをリセットします。

P0、P1コンフィギュレーション・スペース

このタブでは、そのポートのコンフィグレーション空間レジスターを読み出すことができます。各ポートのコンフィグレーション・スペースを含む個別のタブが表示されます。