インテルのみ表示可能 — GUID: msj1621977823812

Ixiasoft

インテルのみ表示可能 — GUID: msj1621977823812

Ixiasoft

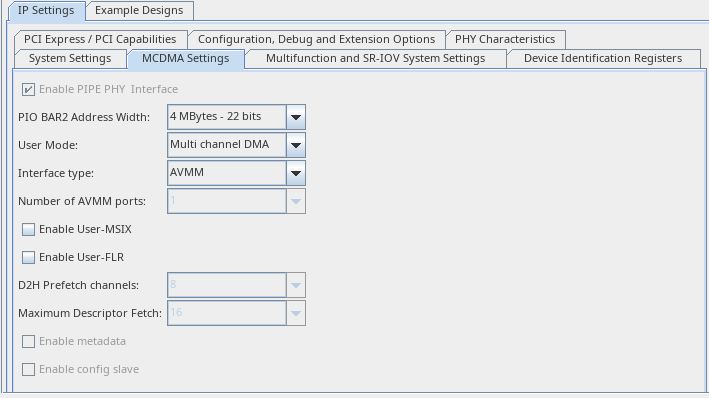

5.1.2. MCDMAの設定

| パラメーター | 値 | 説明 |

|---|---|---|

| PIO BAR2 Address Width |

NA 128 Bytes - 7 bits ~ 8 EBytes - 63 bits |

PIO AVMM ポートのアドレス幅。デフォルトのアドレス幅は 22 ビットです。 |

| User Mode |

Multi channel DMA Bursting Master Bursting Slave BAM+BAS BAM+MCDMA |

このオプションを使用すると、ユーザーは MCDMA IP の動作モードをコンフィグレーションできます。 MCDMA モードには DMA 機能があります。 BAM および BAS は、DMA 機能なしでバーストマスターおよびスレーブ AVMM 機能を提供します。 |

| Interface type |

AVMM AVST |

D2HDM および H2DDM のユーザー・ロジック・インターフェイス・タイプ。 デフォルト: Avalon-MMインタフェース |

| Number of ports |

1 4 |

AVMM インターフェイス・タイプの場合、これは 1 に固定されます。AVST インターフェイス・タイプの場合、1 ポートまたは 4 ポートを選択できます。 |

| Enable User-MSIX |

On / Off |

User MSI-X は、ユーザー・アプリケーションが MCDMA を介して割り込みを開始できるようにします。このオプションは、ユーザーが MCDMA モードを選択した場合にのみ使用できます。 |

| Enable User-FLR |

On / Off |

ユーザー FLR インターフェイスにより、FLR 信号をユーザー側アプリケーションに渡すことができます。 |

| D2H Prefetch channels |

8 16 32 64 128 256 |

D2H プリフェッチ・チャネルを設定します。 AVST 1 ポート・インターフェイスのみに適用されます。 現在のリリースでは、D2H プリフェッチ・チャネル・パラメーターは、IP パラメーター・エディターで選択した合計 256 チャネルまでの DMA チャネルの総数に従います。選択したチャネルの総数が 256 を超える場合、D2H プリフェッチ・チャネルは 64 に固定されます。 |

| Maximum Descriptor Fetch |

16 32 64 |

D2H プリフェッチ・チャネルごとにフェッチされるディスクリプターの最大数を設定します。 AVST 1 ポート・インターフェイスのみに適用されます。 |

| Enable Metadata |

On / Off |

メタデータを有効にします。 AVST 1 ポート・インターフェイスのみに適用されます。 |

| Enable config slave |

On / Off |

このパラメーターは、ユーザーがコンフィグレーションすることはできません。これは、ルート ポート・モードが選択されると自動的にオンになります。エンドポイント・モードには適用されません。 |