インテルのみ表示可能 — GUID: ula1593219899765

Ixiasoft

インテルのみ表示可能 — GUID: ula1593219899765

Ixiasoft

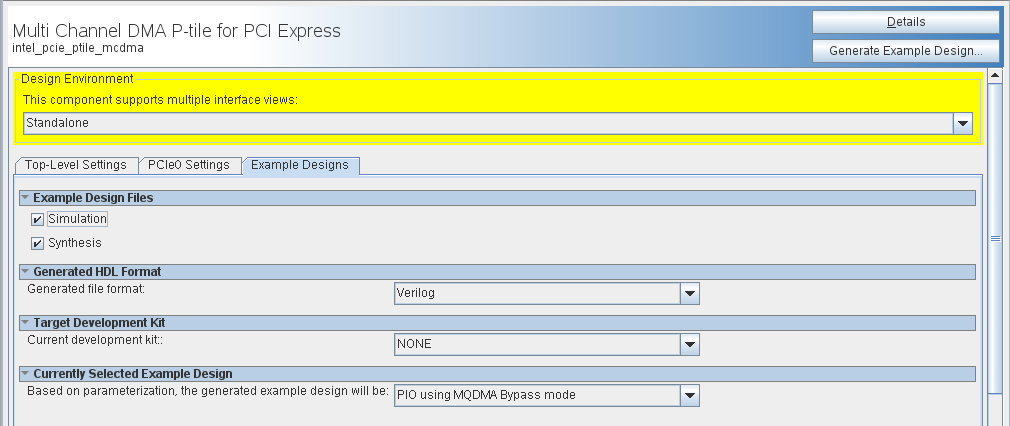

6.3. デザイン例

| パラメーター | 値 | デフォルト値 | 説明 |

|---|---|---|---|

| Simulation |

On / Off |

True |

Simulation ボックスをチェックすると、シミュレーションに必要なすべてのファイルセットが生成されます。このボックスがチェックされていない場合、シミュレーションに必要なファイルセットは生成されません。代わりに、Qsys サンプル デザイン システムが生成されます。

注: シミュレーションでは、複数の物理機能と SR-IOV はサポートされていません。サンプル デザインを生成するときは、シミュレーションをオフにします。

|

| Synthesis |

On / Off |

True |

Synthesis ボックスをオンにすると、合成に必要なすべてのファイルセットが生成されます。合成ボックスがチェックされていない場合、合成に必要なファイルセットは生成されません。代わりに、Qsys サンプル・デザイン・システムが生成されます。 |

| Generated file format |

Verilog |

Verilog |

HDLフォーマット |

| Current development kit |

None インテル® Stratix® 10 DX P-Tile ES 1 FPGA Development Kit Intel Agilex® F-Series P-Tile ES0 FPGA Development Kit Intel Stratix 10 DX P-Tile Production FPGA Development Kit |

このオプションは、リストされているさまざまな開発キットのサポートを提供します。インテル FPGA 開発キットの詳細については、インテル FPGA の ウェブサイトを参照してください。 このメニューがグレー表示されている場合は、選択したオプションでボードがサポートされていないためです (たとえば、合成の選択が解除されている)。 インテルFPGA 開発ボードが選択されている場合、生成に使用されるターゲットデバイスは、開発キットのデバイスと一致するものです。

注: Fタイルの開発キットはサポートされていません。

|

|

| Currently Selected Example Design |

PIO using MQDMA Bypass mode Device-side Packet Loopback Packet Generate/Check AVMM DMA Traffic Generator/Checker External Descriptor Controller |

「User Mode」および「Interface Type」の MCDMA 設定に基づいて、さまざまなサンプル デザインがサポートされます。 サンプル・デザイン・オプションのリストは次のとおりです。 User Mode=MCDMA, Interface Type=AVST:

User Mode=MCDMA, Interface Type=AVMM:

User Mode=Bursting Master:

User Mode=BAM+BAS:

User Mode=BAM+MCDMA, Interface Type=AVMM:

User Mode=BAM+MCDMA, Interface Type=AVST:

User Mode=Data Mover Only:

|