インテルのみ表示可能 — GUID: sss1412046539057

Ixiasoft

1.4.3.3. FPGAコンフィグレーション用のPFLシミュレーションの実行

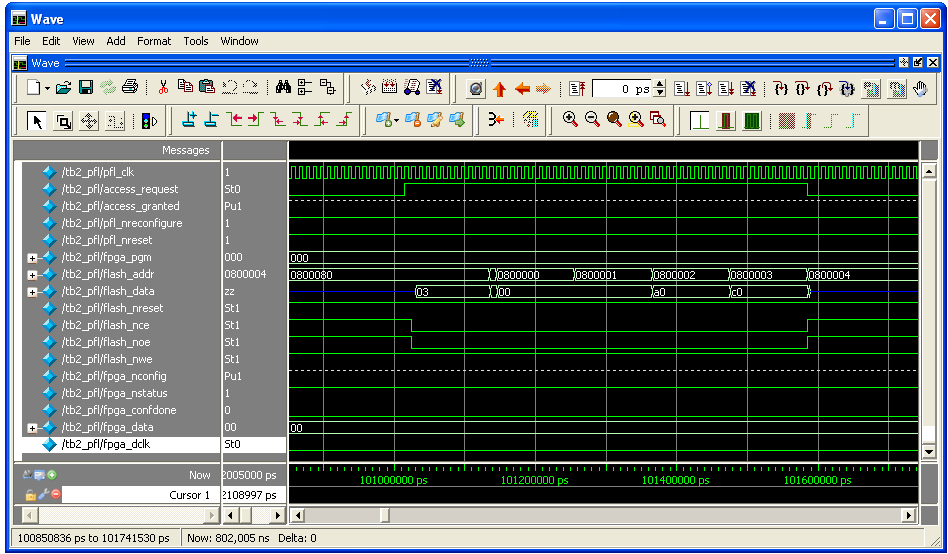

このシミュレーション例におけるオプション・ビット・セクターの開始アドレスと終了アドレスはそれぞれ、0×800000 と 0×800080 です。PFL IPコアでは最初に、最終アドレスである 0×800080 から読み出し、.pof バージョン情報を取得します。fpga_pgm[2..0] が000に設定されている場合、PFL IPコアはアドレス 0×800000 からアドレス 0×800003 を読み出し、ページ0の開始アドレスと終了アドレスおよびPage-Validビットを取得します。アドレス 0×800000 のLSBはPage-Validビットです。

PFL IPコアがFPGAコンフィグレーションを続行するには、Page-Validビットが0である必要があります。PFL IPコアがフラッシュから読み出す間、アクティブLowの flash_nce 信号と flash_noe 信号をアサートし、アクティブHighの pfl_flash_access_request 信号をアサートします。

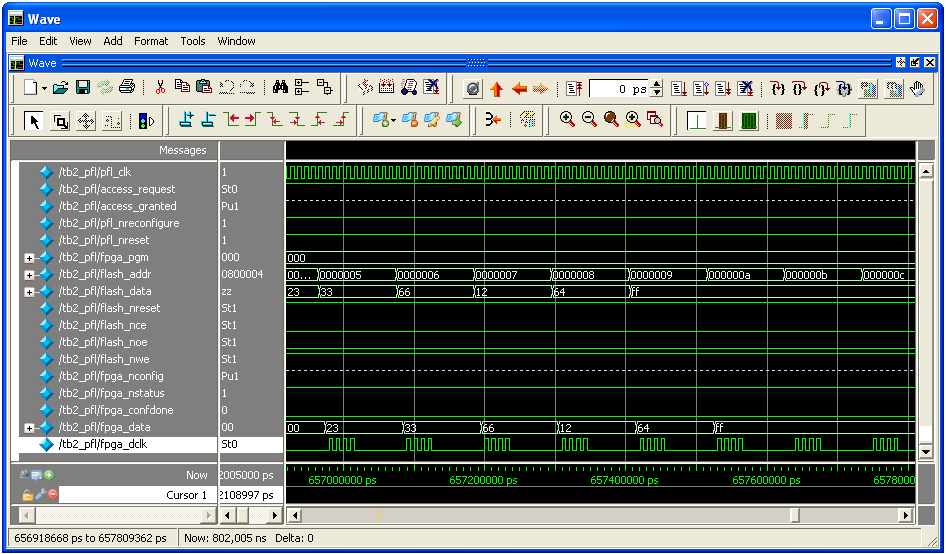

ページ0のオプションビットを読み出した後、コンフィグレーション開始前に、PFL IPコアは一定期間待機します。flash_data は、この期間内に0×ZZのままです。fpga_dclk がトグルを開始すると、コンフィグレーションが開始されます。コンフィグレーション中、PFL IPコアは flash_nce 信号および flash_noe 信号をLowに、pfl_flash_access_request 信号をHighにアサートします。

FPGAのコンフィグレーションは、fpga_conf_done 信号がHighにアサートされるまで続きます。これは、コンフィグレーションが完了したことを示します。コンフィグレーション・プロセスが完了すると、PFL IPコアは flash_nce 信号および flash_noe 信号をHighに引き上げ、pfl_flash_access_request 信号をLowに引き上げることで、コンフィグレーション・データがフラッシュ・メモリー・デバイスから読み出されなくなったことを示します。