インテルのみ表示可能 — GUID: bdw1484178260761

Ixiasoft

インテルのみ表示可能 — GUID: bdw1484178260761

Ixiasoft

7. キャリブレーション

Power-up Calibration、Background Calibration、およびUser Recalibrationがキャリブレーションの主要なタイプとなります。

- パワーアップ・キャリブレーションはデバイス起動時に自動的に開始し、デバイスのコンフィグレーション中に実行します。

- バックグラウンド・キャリブレーションをイネーブルすると、バックグラウンド・キャリブレーションはバックグラウンドで継続的に実行されます。

- ダイナミック・リコンフィグレーションを使用して、ユーザー・リキャリブレーションをトリガーします。この場合、ユーザーが必要なキャリブレーション・シーケンスをイネーブルする必要があります。

インテルQuartus Prime開発ソフトウェアの以前のバージョンから、インテルQuartus Prime開発ソフトウェア・バージョン18.1以降にアップグレードする場合、ネイティブPHY IPは、17.5 Gbps以上のデータレートで動作するHタイルGXTデザイン・トランシーバー・リンクを自動的にEnable background calibrationにアップグレードします。特定の要件およびバックグラウンド・キャリブレーションを制御する方法の詳細については、バックグラウンド・キャリブレーションを参照してください。

インテルStratix 10デバイスは、OSC_CLK_1 ピンを使用して、トランシーバーのキャリブレーション・クロック・ソースを提供します。25、100、または125 MHzのフリーランニングで安定したクロックを OSC_CLK_1 に提供する必要があります。

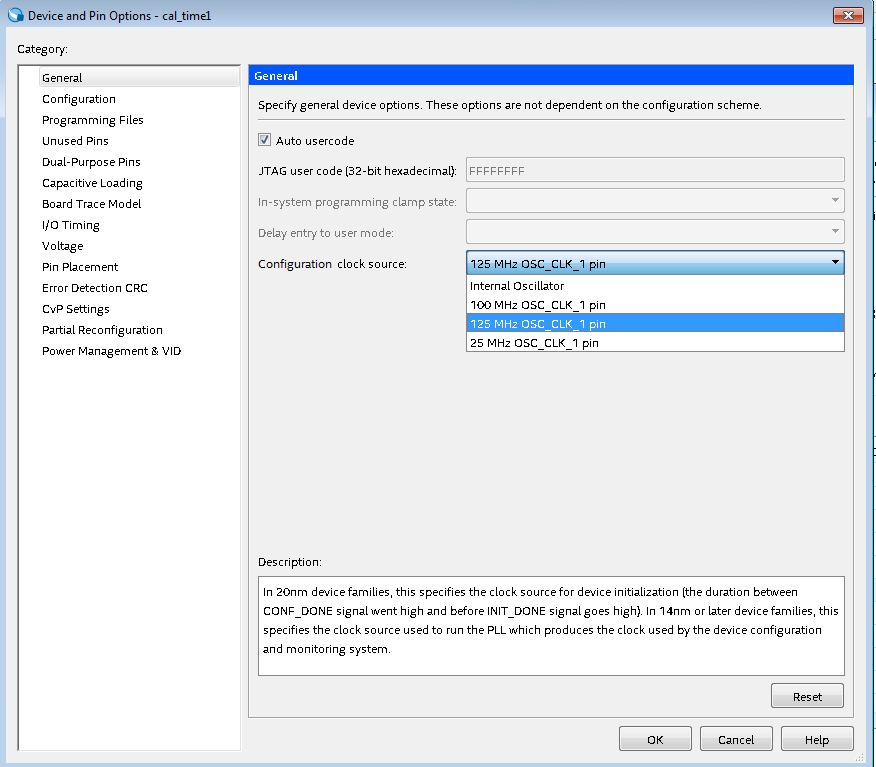

FPGAのInternal Oscillatorは、トランシーバーのキャリブレーションには使用できません。このクロックソースをインテルQuartus Prime設定の中のConfiguration clock sourceとして選択しないでください。

このクロックを提供することに加えて、Quartus assignmentsで適切な周波数も選択する必要があります。

- メニューを下にスクロールします。

- 25、100、または125 MHz OSC_CLK_1 ピンオプションを選択します。

選択したクロックソースが.qsfに次のように表示されます。

set_global_assignment -name DEVICE_INITIALIZATION_CLOCK OSC_CLK_1_125MHz

FPGA内には、OSC_CLK_1 からクロックを受信し、PreSICEに250MHzのキャリブレーション・クロックを提供するPLLがあります。トランシーバーPLL (ATX PLL、fPLL、CDR/CMU PLL) を駆動するすべてのリファレンス・クロックは、FPGAコンフィグレーションを開始する前に安定した周波数を持ち、フリーランニングである必要があります (FPGAの nCONFIG 入力をHighにプルします)。OSC_CLK_1 ピン要件の詳細については、Intel Stratix 10 GX and SX Device Family Pin Connection Guidelinesを参照してください。