インテルのみ表示可能 — GUID: jrj1506278530260

Ixiasoft

インテルのみ表示可能 — GUID: jrj1506278530260

Ixiasoft

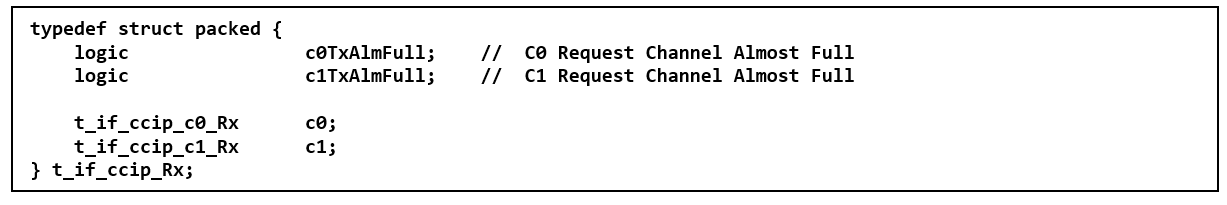

1.3.8. CCI-P Rx信号

Rxチャネルは2つあります。

- チャネル0はメモリー応答、MMIOリクエストおよびUMsgをインターリーブします。

- チャネル1は、Txチャネル1で開始されたAFUリクエストに対する応答を返します。

c0TxAlmFull信号およびc1TxAlmFull信号は、AFUへの入力です。これらはRx信号の構造で宣言されますが、論理的にはTxインターフェイスに属します。そのため、前章において説明されています。

Rxチャネルにはフロー制御がありません。AFUは、生成したメモリーリクエストに対する応答を受け入れる必要があります。AFUは、メモリーリクエストを生成する前にバッファーを事前に割り当てる必要があります。AFUはまた、MMIOリクエストを受け入れる必要があります。

Rxチャネル0には、メモリー応答およびMMIOリクエストに対する個別のValid信号があります。それらのValid信号の1つのみをサイクルに設定できます。MMIOリクエストには、MMIO読み出しとMMIO書き込みに個別のValid信号があります。mmioRdValidもしくはmmioWrValidのどちらかが設定されている場合、そのメッセージはMMIOリクエストであり、t_if_ccip_c0_Rx.hdrをt_ccip_c0_ReqMmioHdrにキャストし処理する必要があります。

| 信号 | 幅 (ビット) | 方向 | 説明 |

|---|---|---|---|

| pck_cp2af_sRx.c0.hdr | 28 | 入力 | チャネル0の応答ヘッダーもしくはMMIOリクエストヘッダー。 表 21 を参照してください。 |

| pck_cp2af_sRx.c0.data | 512 | 入力 | チャネル0データバスのメモリー読み出し応答とUMsg。

MMIO書き込みリクエスト

|

| pck_cp2af_sRx.c0.rspValid | 1 | 入力 | 1に設定されている場合、チャネル0のヘッダーとデータが有効であることを示します。ヘッダーは、メモリー応答として解釈され、resp_typeフィールドをデコードする必要があります。 |

| pck_cp2af_sRx.c0.mmioRdValid | 1 | 入力 | 1に設定されている場合、チャネル0のMMIO読み出しリクエストを示します。 |

| pck_cp2af_sRx.c0.mmioWrValid | 1 | 入力 | 1に設定されている場合、チャネル0のMMIO書き込みリクエストを示します。 |

| 信号 | 幅 (ビット) | 方向 | 説明 |

|---|---|---|---|

| pck_cp2af_sRx.c1.hdr | 28 | 入力 | チャネル1の応答ヘッダー。表 21 を参照ください。 |

| pck_cp2af_sRx.c1.rspValid | 1 | 入力 | 1に設定されている場合、チャネル1のヘッダーは有効な応答であることを示します。 |